# **Abschlussbericht**

für das BMBF Verbundprojekt

# Energie-effiziente Leistungsbauelemente für den Spannungsbereich bis 400V

## **SuperPowerMOS**

Förderkennzeichen: 13N9616

Teilvorhaben

Fraunhofer Institut für Siliziumtechnologie ISIT

Technologische Teilschritte und Bauelementesimulationen für neuartige PowerMOS Bauelemente

**Dezember 2011**

Projektleiter: Detlef Friedrich, Henning Hanssen

## 0. Kurzdarstellung

#### 1. Aufgabenstellung

Die Zielsetzung des Projekts bestand in der Prozess/Verfahrensentwicklung für die Herstellung von PowerMOS-Kompensationsbauelementen für den Spannungsbereich bis 400V. Hierbei stand die Reduzierung des Einschaltwiderstandes zur Erhöhung der Bauelemente-Effizienz im Vordergrund.

Es wurden 3 verschiedene Bauelementeansätze untersucht:

- 1. Trenchbasierte SuperPowerMOS Bauelemente nach dem Dual-Gate Prinzip

- 2. Trenchbasierte SuperPowerMOS Bauelemente nach dem Split-Gate Prinzip

- 3. Trenchbasierte Super-Junction Bauelemente mittels Epitaxie

Für alle drei Ansätze wurden ausführliche Bauelementesimulationen durchgeführt, auf deren Grundlage Maskenlayout und Technologieablauf erstellt wurden. Die technologische Verifikation hat zu ersten Bauelemente-Prototypen geführt.

#### Zu 1. Dual-Gate Bauelemente

Es wurden Prototypen für 250V Dual-Gate Bauelemente mit unterschiedlichen Designund Technologievarianten hergestellt. Eine besonderere Herausforderung des Dual-Gate Prinzips auf Basis einer trenchbasierten Feldplatten Kompensation stellt die Beherrschbarkeit der mechanischen Spannung während des gesamten Prozessablaufs dar. Tiefe Si-Gräben gefüllt mit einem Isolationsoxid und einer leitfähigen Poly-Si Feldplatte verursachen auf Grund unterschiedlicher thermischer Ausdehnungskoeffizienten insbesondere bei Hochtemperaturprozessen starke mechanische Spannungen, die sogar zu Rissbildungen im Si-Substrat führen können. Damit eng korreliert sind erhöhte Leckströme im Sperrfall des Bauelementes. Eine wesentliche Erkenntnis wurde gewonnen aus der Korrelation elektrischer Ergebnisse mit Design und Technologieparametern. Die Zielsetzung den Einschaltwiderstand um den Faktor 3 zu reduzieren konnte erfolgreich nachgewiesen werden mit minimalen spezifischen R<sub>Dson</sub>-Werten von 3,3mOhmcm² für Bauelemente der Spannungsklasse 250V.

#### Zu 2 Split-Gate Bauelemente

Es wurden Simulationen durchgeführt sowie unterschiedliche Designvarianten für 250V Split-Gate Bauelemente erstellt. Ein erster Technologiedemonstrator wurde hergestellt mit einer Si Grabentiefe von ca.17µm, der zur Bewertung der technologischen Risiken diente. Auch hier gilt, wie auch für den Dual Gate Ansatz, die mechanischen Spannungen bei Verwendung tiefer Feldplattenstrukturen beherrschbar zu machen. Unter Berücksichtigung der Marktanforderungen und den vorhandenen technologischen Risiken wurde für die Prototypenherstellung die Spannungsklasse bis 100V in den Vordergrund gestellt. Ein erster Split-Gate Demonstrator wurde erfolgreich hergestellt.

#### Zu 3 Trenchbasierte Super-Junction (SJ) Bauelemente

Im Gegensatz zur Feldplattenkompensation erfolgt beim Super-Junction Ansatz die Kompensation durch die Raumladung von säulenförmigen pn-Strukturen, die mittels

epitaktisch gefüllter Si-Gräben realisiert werden. Hierbei treten keine mechanische Spannungen auf, da die pn-Säulenstrukturen vollständig aus Si bestehen.

Hierfür waren umfangreiche Technologieentwicklungen erforderlich z.B. das Trockenätzen tiefer Si-Gräben bis 25µm Trenchtiefe sowie deren Auffüllung mittels epitaktischem in situ dotiertem Si. Eine besondere Herausforderung stellt hierbei die kontrollierte Einstellung der Dotierungskonzentration dar.

Es wurden umfangreiche Simulationen durchgeführt, auf deren Grundlage unterschiedliche Bauelemente Layouts erstellt wurden. In ersten Technologiedurchläufen wurde ein vollständiger Technologiedemonstrator hergestellt.

#### 2. Vorhabensvoraussetzung

Die Forschung und Entwicklung von Leistungsbauelementen ist seit Errichtung des ISIT in Itzehoe vor ca. 15 Jahren ein Schwerpunktthema des Instituts. Eine besondere Relevanz erhält dieser Themenschwerpunkt durch die Zusammenarbeit mit dem Industriepartner Vishay und der Verfügbarkeit einer Produktionstechnologie für Leistungsbauelemente sowie einem daraus resultierenden industriellen Anwendungsbezug.

Die wachsende Bedeutung der Leistungselektronik in den vergangenen Jahren im Hinblick auf F&E-Themen zur regenerativen Energie, Elektromobilität und innovativen Leistungssystemen hat auch die Entwicklung von energie-effizienten Leistungsbauelementen aufgrund der wachsenden Konkurrenzsituation stark motiviert.

Das ISIT verfügt als Voraussetzung zu diesem Verbundprojekt über langjährige Erfahrungen auf dem Gebiet der Si-Bauelemente Technologie,- Physik und – Design und hat mehrere Verbundprojekte zu diesem Thema koordiniert.

#### 3. Planung und Ablauf des Vorhabens

Die Planung des Vorhabens im Konsortium wurde durch 2-3 Projekttreffen pro Jahr sichergestellt (insgesamt 9 Treffen), zu denen auch der Projektträger eingeladen war und regelmässig teilgenommen hat. Die Treffen fanden überwiegend in Itzehoe statt, jedoch wurde jeweils einmal bei jedem Partner ein Projekttreffen veranstaltet.

Zur weiteren effizienten Planung der Arbeiten mit dem Industriepartner Vishay wurden, Dank der räumlichen Nähe, wöchentliche Treffen mit dem Kernteam von Vishay und ISIT durchgeführt.

Ebenfalls fanden weitere Arbeitstreffen mit der Fa. Danfoss statt, bei denen auch konkrete Laborarbeiten zur Analyse von Aufbauten gemeinsam durchgeführt wurden.

Die Zeit- und Kostenplanung des Projekts wurde weitgehend gemäß der Antragstellung umgesetzt. Als Folge starker konjunktureller Schwankungen in den Jahren 2009-2010, verbunden mit personellen Engpässen, wurde eine kostenneutrale Projektverlängerung von 3 Monaten erforderlich.

#### 4. Wissenschaftlicher und technischer Stand, an den angeknüpft wurde

Das Kompensationsprinzip für Hochvolt PowerMOS Transistoren geht zurück auf eine Patentschrift (US 005216275A) von X. Chen aus dem Jahre 1993, mit dem Titel "Semiconductor power devices with alternating conductivity type high voltage breakdown regions".

Eine erste technologische Realisierung von Kompensationsbauelementen wurde von Infineon 2001 vorgestellt und mit dem Innovationspreis der Deutschen Wirtschaft gewürdigt. Bauelemente dieser Art werden seit ca. 2002 unter dem Produktnamen CoolMOS für die 600 V Spannungsklasse am Markt angeboten.

Die technologische Realisierung für die Herstellung der Dotierungssäulen des CoolMOS-Bauelementes basiert auf einem Ansatz mehrfacher Lithographie-, Implantations- sowie Epitaxieschritte. Hierbei ist der technologische Aufwand für die Herstellung von CoolMOS Transistoren erheblich und hat daher zu alternativen technologischen Ansätzen geführt. Des Weiteren ist, bedingt durch das Herstellungsverfahren der Multi-Epitaxie, die CoolMOS- Technologie geometrisch nur begrenzt skalierbar. Das bedeutet, der  $R_{DSon}$  Wert von CoolMOS für Spannungswerte < 400 V ist gegenüber Standard-PowerMOS zwar niedriger, erreicht aber nicht die geringen  $R_{DSon}$  Werte trenchbasierter Bauelemente auf Basis der Feldplattenkompensation.

Infineon war anfänglich der einzige Anbieter von Hochvolt-PowerMOS-Bauelementen basierend auf dem Super-Junction-Kompensationsprinzip. In den Jahren nach der Markteinführung sind weitere Anbieter (z.B. Toshiba, IR ) für 600V Bauelemente hinzugekommen.

Ein erster Ansatz für Kompensationsbauelemente der Spannungsklasse 200V wurde in 2007 auf der ISPSD Konferenz (International Symposium on Power Semiconductor Devices) von den Forschungseinrichtungen der japanischen Firmen Denso Corporation und Toyota vorgestellt. Der Ansatz basiert auf selektiver Epitaxie zur Erzeugung der Kompensationsstrukturen.

#### 5. Zusammenarbeit mit anderen Stellen

Innerhalb des Projektkonsortiums war der Hauptpartner des ISIT die Fa. Vishay Siliconix Itzehoe GmbH. Als Hersteller von PowerMOS Bauelementen und als unmittelbarer Industriepartner des ISIT sind beide Seiten an einer engen Zusammenarbeit im Bereich innovativer F&E-Themen interessiert. Hier basiert die Zusammenarbeit auf unterstützende F&E-Themen im Hinblick auf die zukünftige Fertigung neuer Bauelemente Generationen.

Ebenso ist die enge Zusammenarbeit mit der Fa. Danfoss Silicon Power hervorzuheben. Als Hersteller von Leistungsmodulen ist die Fa. Danfoss der nächstgelegene Partner der Bauelementeentwicklung in der aufsteigenden Wertschöpfungskette. Die enge Zusammenarbeit bezog sich auf F&E Themen der Bauelementecharakterisierung und Analytik sowie der technologischen Anpassung der Chipmetallisierung, die in Verbindung mit der Aufbautechnik steht.

Eine enge Zusammenarbeit mit dem Industriepartner Siltronic fand vorrangig mit der Fa. Vishay im Hinblick auf neue Verfahren der Si-Substratherstellung für PowerMOS Anwendungen statt.

| 0. Kurzdarstellung                                                    | 2  |

|-----------------------------------------------------------------------|----|

| 1. DUAL-GATE BAUELEMENTE                                              | 6  |

| 1.1 Einleitung                                                        | 6  |

| 1.2 Prozess- und Device-Simulation.                                   |    |

| 1.3 Maskenlayout                                                      |    |

| 1.3.1 Design der Feldplatten-Kompensationsbauelemente                 |    |

| 1.3.2 Testmaske für Stressuntersuchung                                |    |

| 1.4 Herstellungstechnologie von Kompensations-Dioden und Transistoren |    |

| 1.4.1 Wafer-Substrat und Epitaxie Spezifikation                       |    |

| 1.4.2 Stressuntersuchungen                                            |    |

| 1.4.3 Herstellungsprozess                                             |    |

| 1.5 Elektrische Charakterisierung                                     | 21 |

| 1.6 Zusammenfassung                                                   | 25 |

| 2. SPLIT-GATE BAUELEMENTE                                             | 26 |

| 2.1 Einleitung                                                        | 26 |

| 2.2 Simulation und Bauelemente Design                                 |    |

| 2.3 Herstellungstechnologie für Split-Gate Bauelemente                |    |

| 2.3.1 Herstellung eines Technologiedemonstrators                      |    |

| 2.3.2 Herstellung erster Split-Gate Bauelemente                       |    |

| 2.4 Elektrische Charakterisierung                                     |    |

| 2.5 Zusammenfassung                                                   | 39 |

| 3. SUPER-JUNCTION BAUELEMENTE                                         | 40 |

| 3. 301 ER JOINE HOIN DI ROLLEINEINTE                                  |    |

| 3.1 Einleitung                                                        |    |

| 3.2 Simulation                                                        |    |

| 3.3 Maskendesign                                                      |    |

| 3.4 Technologieentwicklung                                            |    |

| 3.4.1 Driftzonenepitaxie                                              |    |

| 3.4.2 Atzen tieler Graben                                             |    |

| 3.4.4 Planarisierung der Si-Oberfläche durch CMP                      |    |

| 3.5 Technologiedemonstrator                                           |    |

| 3.6 Zusammenfassung                                                   |    |

| Literaturhinweis                                                      | 57 |

| Due l'alitte a un                                                     | F0 |

| Projektteam                                                           | 59 |

## 1. Dual-Gate Bauelemente

## 1.1 Einleitung

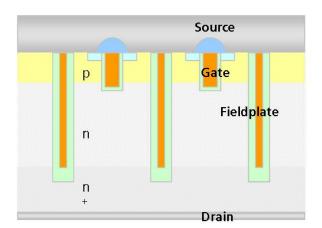

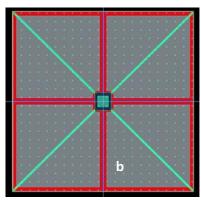

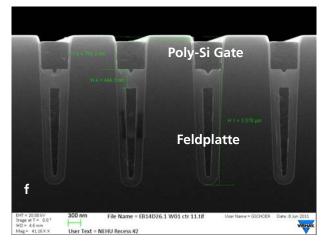

Die Entwicklung von Hochvolt Dual Gate Bauelementen nach dem Feldplatten Kompensationsprinzip, gemäß Abb. 1.1, erfolgte auf der Grundlage von umfangreichen Prozess- und Device-Simulationen. Aus diesen Ergebnissen wurden Bauelementedesigns erarbeitet und in ein Maskenlayout umgesetzt.

Die Spezifikationen für das Wafersubstrat wurde festgelegt und der Aufbau der mehrstufigen Epitaxie für die Driftzone wurde definiert. Des Weiteren wurde die Technologie für die feldplattenbasierten Kompensationsstrukturen entwickelt. Hierbei standen die Entwicklung der Ätzprozesse von 12 µm bis 20 µm tiefen Si-Gräben, deren Auffüllung mit einem LPCVD-Oxid (TEOS) und in situ dotiertem amorphen-Si, sowie die Planarisierung der gefüllten Trenchstrukturen mittels CMP im Vordergrund.

Es hat sich gezeigt, dass die in eine Richtung orientierten Kompensationsstrukturen durch thermische Fehlanpassung bei den Auffüllprozessen sowie bei den nachfolgenden Hochtemperaturprozessen eine hohe mechanische Spannung entwickeln, die eine umfangreiche Stressuntersuchung erforderlich gemacht haben.

Zur Verifikation des Kompensationsansatzes wurden Dioden und Transistoren hergestellt und elektrisch charakterisiert. Hierbei konnte die Richtigkeit des Kompensationsansatzes bestätigt werden. Es wurden Regeln für ein Redesign hergeleitet, die in dem Layout eines zweiten Maskensatzes berücksichtigt wurden.

Auf der Grundlage eines zweiten Maskensatzes wurden Feldplatten Kompensationstransistoren der 2. Generation hergestellt, die eine verbesserte Auslegung im Hinblick auf geometrische Stresskompensation sowie verbesserte elektrische Kompensation im Chiprandbereich aufweisen. Die weitere Optimierung der Bauelemente-Eigenschaften wurde durch das Redesign einzelner Masken, durch die Modifikation des Prozessablaufs und durch die Anpassung einzelner Prozessschritte erreicht.

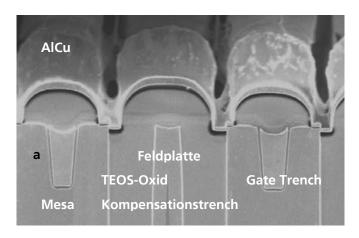

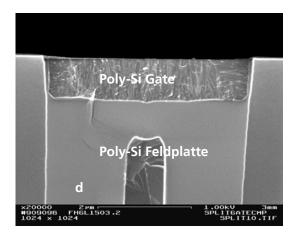

Abb.1.1: Dual Gate Struktur mit Gate Trench und Feldplatten Kompensation

#### 1.2 Prozess- und Device- Simulation

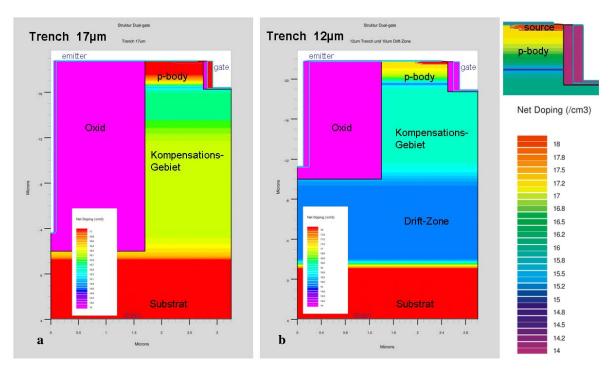

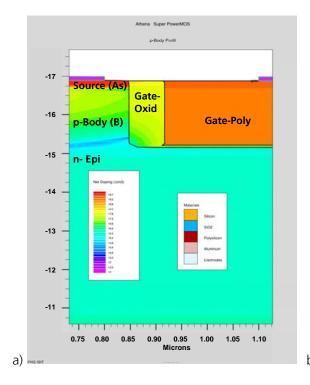

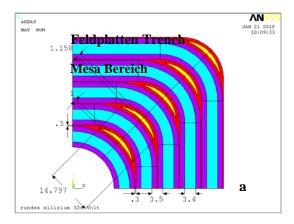

Die Zielsetzung der Prozess- und Bauelementesimulation (Silvaco: ATHENA und ATLAS) war die Festlegung der Geometrie der Kompensationsstruktur des Dual Gate Transistors. Simuliert wurden die elektrischen Eigenschaften von Transistoren mit Feldplatten unterschiedlicher Trenchtiefe gemäß Abb.1.2. Unter der Randbedingung eines optimalen Dotierungsprofils der n-dotierten Driftzone mit höchstmöglicher Dotierungskonzentration wurden Durchbruchspannung von 250V bzw. 290V erreicht.

Abb. 1.2: Darstellung der simulierten Transistorzelle mit Feldplattenkompensation a) Feldplattenkompensation mit 17µm tiefer Kompensationsstruktur

b) Feldplattenkompensation mit 12µm tiefer Kompensationsstruktur

Dotierungskonzentration der epitaktischen Driftzone ermöglicht Durchlassbetrieb des Bauelementes einen kleinen Einschaltwiderstand R<sub>DSon</sub>. Im Sperrbetrieb soll durch die Kompensationswirkung der Feldplatte eine ausreichende Spannungsfestigkeit des Bauelementes gewährleistet werden. Eine mehrstufige epitaktische Driftzone, mit abnehmender Dotierungskonzentration zur Oberfläche, verbessert die Verarmung in der Raumladungszone und erhöht die Durchbruchsspannung. Die Kompensationseigenschaften sind außerdem von den geometrischen Parametern des Grabens, d.h. der Tiefe und dem Abstand (Mesa) sowie der Dicke der Isolationsschicht abhängig. Bei einer angestrebten Durchbruchspannung von 250V wird eine Schichtdicke des Isolationsoxides von 1.6 um benötigt. Hinzu kommt eine Feldplatte mit einer Schichtdicke von ca. 400-600nm. Hieraus ergibt sich eine Trenchbreite von 3,6 µm bis 3,8µm.

Um den Effekt der Feldplatten Kompensation qualitativ zu verstehen, kann man wie in der Theorie des Langkanal-MOS-Transistors als Näherung ansetzen, dass die Feldplatte eine Ladung in der Raumladungszone influenziert, die nur von der y-Richtung parallel zum Gate bzw. hier zur Feldplatte abhängt. Die Simulationen zeigen, dass bei einer optimal

konstruierten Struktur die Equipotential-Linien in der Nähe der Durchbruchspannung tatsächlich senkrecht zum Oxid-Interface verlaufen.

Die Kompensationsladung  $Q_{comp}$  lässt sich aus der kapazitiven Spannungsteilung zwischen Oxidkapazität  $\epsilon_{ox}$  / $d_{ox}$  und Halbleiter-Kapazität  $\epsilon_{si}$  /( $w_{si}$  /2) berechnen. Die Dicke des Si-Kondensators ist die halbe Mesa-Breite  $w_{si}$ , weil wegen der Symmetrie die laterale Feldstärke in der Mitte des Si-Mesa zu Null wird. Man erhält:

$$Q_{comp} = \frac{\varepsilon_{si}V(y)}{\frac{w_{si}}{2} + \frac{\varepsilon_{si}}{\varepsilon_{ox}}d_{ox}}$$

(1)

Und für die Halbleiter-Ladung:

$$Q_{HL} = \frac{w_{si}}{2} N_D \tag{2}$$

V(y) ist die Spannung zwischen der auf p-Body-Potential (Null) liegenden Feldplatte und der Spannung in der Tiefe y in der Drift-Zone.

Die Wahl der Dicke des Oxids  $d_{ox}$  ist dadurch bestimmt, dass es die Potentialdifferenz am Ende der Feldplatte, zzgl. eines Sicherheitsfaktors wegen der Feldüberhöhung an der Plattenkante, aushalten muss. Deshalb sind die beiden Geometrie-Terme in Gl.(1) von ähnlicher Größe. In der Poisson-Gleichung wird  $Q_{HL}$ -  $Q_{comp}$  eingesetzt.  $Q_{comp}$  trägt zur "Glättung" des Feldstärkeverlaufs bei. Von Kompensation spricht man, wenn die Raumladungszone beim Durchbruch bis an das untere Ende des Kompensationsgrabens reicht und im optimalen Fall einen trapezförmigen Verlauf, begrenzt durch das hochdotierte Substrat, zeigt. Dann ist bei vorgegebener Weite der Raumladungszone die Durchbruchspannung am höchsten.

Abweichend sind 2 Fälle zu unterscheiden:

## Unterkompensation, d.h. $Q_{comp} < Q_{HL}$ :

Wenn die Mesa-Breite oder Oxid-Dicke zu groß gewählt werden, nähert man sich dem Fall eines einfachen Halbleiter-pn-Übergangs und der Durchbruch erfolgt an der Oberfläche und damit auch in der Nähe des Gateoxids.

## Überkompensation, d.h. $Q_{comp} > Q_{HL}$ :

Setzt man die Terme nach Gl.(1) und Gl.(2) in eine 1-dimensionale Poisson-Gleichung ein, so findet man, dass die maximale Feldstärke und damit der Durchbruch am Boden der Drift-Zone auftritt.

Die Simulation sucht nun eine Geometrie, die es erlaubt, ein möglichst großes  $Q_{HL}$  zu kompensieren.  $R_{DSon}$  ist nämlich proportional zum Kehrwert von  $Q_{HL}$ , da in dem hier interessierenden Spannungsbereich der Widerstand der Driftzone dominiert.

Beim Design ist ferner zu beachten, dass es auch eine "konstitutionelle" Unterkompensation gibt. In der Nähe des p-Body pn-Übergangs ist V(y) noch klein, sodass man  $Q_{HL}$  dadurch verringern sollte, dass man eine Mehrschicht-Epitaxie für die Si-Driftzone benutzt und zwar mit geringerer Dotierung an der Oberfläche.

Eine konstitutionelle Überkompensation entsteht dagegen in konkaven Ecken von 3D-Feldplattenstrukturen. Dann tragen Platten aus 2 Richtungen zu  $Q_{comp}$  bei und es tritt ein früher Durchbruch am Boden der Driftzone auf.

Die Simulationen zeigen, dass Strukturen, in denen die gesamte Driftzone kompensiert wird, theoretisch das geringste R<sub>DSon</sub> ermöglichen. Wenn es sich allerdings zeigt, dass die mechanischen Spannungen in einem Oxid ausreichender Dicke technologisch nicht beherrschbar sind, muss man zu Designs übergehen, die nur einen Teil der Driftzone kompensieren. So kann man in der in Abb.1.2 gezeigten 12um-Struktur, die Oxid-Dicke von 1.6um auf 1.1um verringern, weil auf Höhe des Trench-Bodens erst ein Teil der Sperrspannung abgefallen ist. Natürlich geht das auf Kosten von R<sub>DSon</sub>, da die nicht kompensierte Driftzone deutlich niedriger dotiert sein muss.

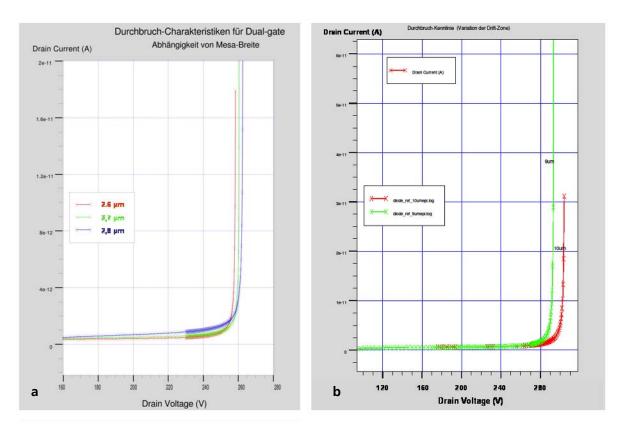

Die folgende Abb. 1.3 zeigt am Beispiel einer zweistufigen epitaktisch erzeugten Driftzone die Abhängigkeit der Durchbruchspannung vom Abstand der Kompensationsstrukturen (Mesabreite).

Abb. 1.3: Simulation der Durchbruchscharakteristik für unterschiedliche Tiefen der Kompensationsstruktur

- a) Typ:17μm Trench, Mesabreiten: 2,6 -2,8 μm

- b) Typ:12µm Trench, Driftzone: 9 µm und 11µm

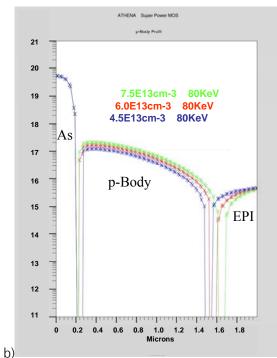

Die Simulation der Schwellspannung erfolgte durch Variation der Bor-Implantationsdosis unter Berücksichtigung des thermischen Budgets der nachfolgenden Prozessschritte. Die Abb.1.4a zeigt den Ausschnitt des simulierten Bauelementebereichs, der aus Symmetriegründen einer halben Transistorzelle (1/2 Mesa) entspricht. Rechts dargestellt ist der Transistortrench mit einer Tiefe von 1,8µm. Die Gateoxiddicke beträgt 70nm. Links angeordnet sind die Implantationsgebiete für Source und p-Body sowie die darunterliegende epitaktische n-Driftzone.

Abb.1.4: Zweidimensionale Simulation der Schwellspannung des SuperPower MOS Transistors a) Ausschnittsvergrößerung der simulierten Struktur: Source, p-Body und Gatebereich b) Implantationsprofil des Source(As), p\_Body und n-EPI-Gebietes

Die Berechnung der Bor-Profile (p-Body) im Bereich des vertikalen Transistors zeigt nach allen relevanten Hochtemperatur-Prozessschritten, in Abhängigkeit von der Implantationsdosis, eine maximale Tiefe von 1,7µm (Abb. 1.4b) Die Device-Simulationen mit Atlas ergeben Schwellspannungen im Zielbereich von 3 bis 4 Volt (Tab. 1.1).

| p-Body | Energie | Dosis            | Vth | Tiefe |

|--------|---------|------------------|-----|-------|

|        | KeV     | cm <sup>-3</sup> | V   | μm    |

| Bor    | 80      | 4,50E+13         | 3,0 | 1,5   |

| Bor    | 80      | 6,00E+13         | 3,5 | 1,6   |

| Bor    | 80      | 7,50E+13         | 4,0 | 1,7   |

Tab. 1.1 : Simulation der Schwellspannung V<sub>T</sub> bei Variation der p-Body Implantationsdosis

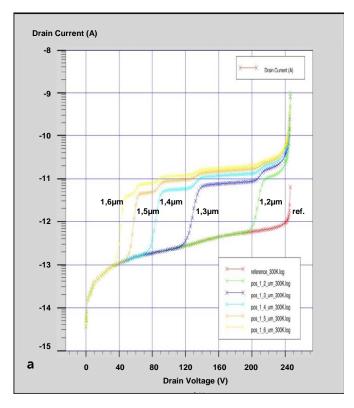

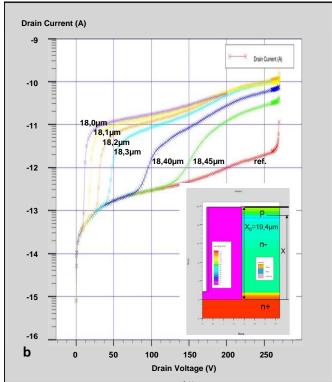

Abb. 1.5: Simulation von Durchbruch-Kennlinien mit Gebieten erhöhter Dichte von Generationszentren a) Generationszentren am Trenchboden im Abstand bis 1.6um.

b) Generationszentren oberhalb des p-Body pn-Übergangs nahe der Si-Oberfläche im Abstand bis 18µm von der unteren Trenchkante

Das wichtigste F&E Thema bei der Untersuchung feldplattenbasierter Kompensationsbauelemente war der hohe Sperrstrom im Zusammenhang mit den tiefen Trenchstrukturen, der bei Dioden- und Transistoren in gleicher Weise nachweisbar war. Es wurde beobachtet, dass der Leckstrom bereits vor dem eigentlichen Avalanchedurchbruch, abweichend von der klassischen Sperrkennlinie, bei unterschiedlichen Spannungswerten einen abrupten Anstieg zeigte. In diesem Zusammenhang wurde versucht den beobachteten Effekt durch Simulation nachzubilden. Hierbei wurde von der Annahme ausgegangen, dass der Leckstrom durch entsprechende Verteilung von Generationszentren entlang der Trenchkante hervorgerufen sein könnte, deren Ursache durch Ätzschädigungen des Kristalls infolge der Trenchätzung, oder durch Kristalldefekte infolge mechanischen Stress, bedingt sein könnten. Der Überlegung folgend, dass die Generation von Leckstrom durch Valenz-Leitungsbandübergänge via Generationszentren innerhalb einer Raumladungszone erfolgt, wurden in der Simulation Zentren entlang der Trenchkante in unterschiedlichem Abstand von der unteren Trenchkante platziert.

Die Abb. 1.5a zeigt simulierte Sperrkennlinien von SuperPowerMOS Dioden, bei denen die Zentren im Abstand bis 1,6µm von der unteren Trenchkante lokalisiert wurden. In der Abb. 1.5 b werden Sperrkennlinien dargestellt, bei denen die Zentren oberhalb des pn-Übergangs, im Abstand bis ca.19µm von der unteren Trenchkante platziert wurden. Die Geometrie der simulierten Struktur ist in dem eingefügten Bild der Abb. 1.5 b dargestellt. Der spannungsabhängige Anstieg des Leckstromes erfolgt sobald sich die Raumladungs-

zone in den Bereich der Generationszentren ausbreitet. Die simulierten Kurven bilden mit überraschender Genauigkeit die gemessenen Sperrstromverläufe ab.

Im Rahmen der Technologieentwicklung wurden erhebliche Anstrengungen unternommen "Defektdichten" im Sinne von Generationszentren zu reduzieren. Hierfür wurden unterschiedliche Ätzprozesse und Seitenwand-Glättungsmethoden erprobt sowie Reduzierungen der Trenchtiefe und der Dicke des Feldplatten-Isolationsoxides vorgenommen.

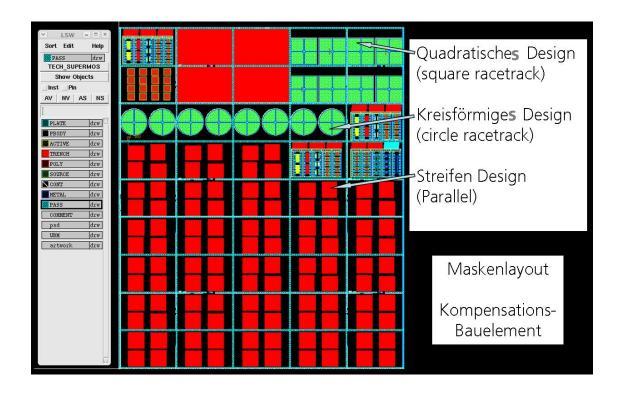

## 1.3 Maskenlayout

Die Lithographie-Maskensätze zur Entwicklung der Kompensationsbauelemente wurden mit dem Design-Tool CADENCE am ISIT entworfen. Die Herstellung der Masken erfolgte extern. Grundsätzlich ist für jeden Technologieansatz ein eigener Maskensatz notwendig. Für die Untersuchung der mechanischen Spannung von tiefen Trenchstrukturen in Abhängigkeit der Device-Geometrie wurde eine spezielle Testmaske angefertigt. Der Maskenentwurf für den Feldplatten-Ansatz wurde im 1. Redesign komplett überarbeitet, unter Berücksichtigung geeigneter Device-Geometrien zur Reduzierung des mechanischen Stress. Darüber hinaus wurden unterschiedliche Varianten für die 3D-Kompensation an Bauelementeecken berücksichtigt. Im weiteren Projektablauf wurden einzelne Maskenebenen durch verbesserte Masken ausgetauscht.

### 1.3.1 Design der Feldplatten-Kompensationsbauelemente

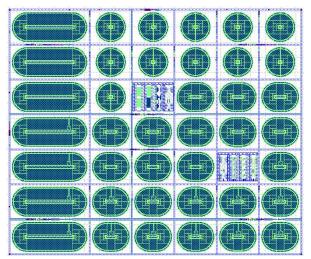

Der Maskensatz zur Herstellung von Transistoren besteht aus 8 Ebenen (PLATE, ACTIVE, TRENCH, POLY, SOURCE, CONTAKT, METAL und PASS). Im Layout wurden Transistoren und Dioden mit unterschiedlichen Geometrien realisiert. Zur Prozesskontrolle wurden außerdem spezielle Test-Strukturen implementiert.

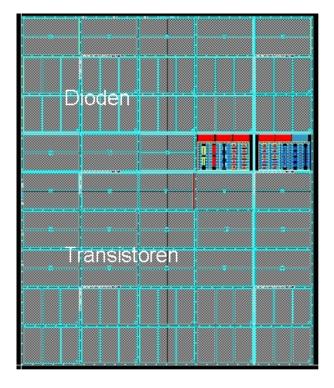

Abb. 1.6: Layout-Übersicht: Anordnung der Transistoren (unten), Dioden (oben) und Test-Felder (rechts) sowie Darstellungen des Chiplayouts

Eine Gesamtübersicht des Maskenlayouts sowie die Darstellung der unterschiedlichen Chiplayouts wird in der Abbildung 1.6 vorgestellt.

Die Kompensationsstrukturen der Transistoren sind als Streifendesign ausgelegt mit einer Breite von 3,6  $\mu$ m oder 3,8  $\mu$ m. Der Abstand der Gräben (Mesabreite) variiert zwischen 2,9  $\mu$ m und 3,3  $\mu$ m.

Der Einfluss der Randgeometrie auf die elektrischen Bauelementeeigenschaften wurde durch Variation der Eckenradien sowie des Abstands der Source-Metallisierung zu der äußeren Kompensationsstruktur untersucht. Dazu wurden verschiedene Geometrie-Typen sowohl für Transistoren als auch für Dioden entworfen. Die Kompensationsstruktur wurde an den Ecken der Bauelemente entweder rechtwinklig oder mit kleinem bzw. großem Radius ausgeführt (Geometrie-Typ-Bezeichnung: Sharp-, Small- und Big- Corner).

#### 1.3.2 Testmaske für Stressuntersuchung

Basierend auf den Erfahrungen mit dem ersten Maskensatz, im Bezug auf stressbedingte Waferverbiegung infolge der einheitlichen Orientierung der tiefen Trenchstrukturen der Streifen-Layouts, wurde eine grundlegende Untersuchung bezüglich der layoutbedingten Stressentwicklung durchgeführt.

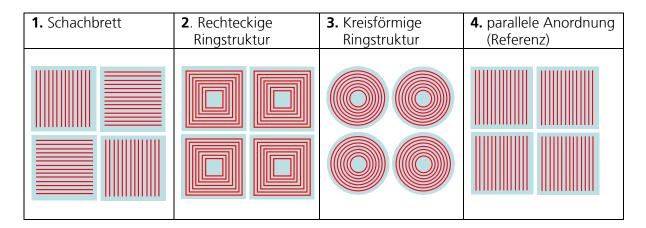

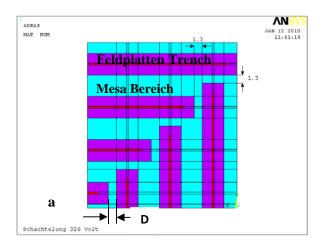

Das Ziel war, durch eine geschickte Anordnung der Gräben, eine Stresskompensation zu erreichen. Geeignete Geometrien wurden zunächst mit Hilfe einer speziellen Testmaske erprobt. Die nachfolgende Tabelle 1.2 fasst die in der Maske vorgesehenen Trench-Geometriealternativen zusammen.

Tab. 1.2: Schematische Darstellung von unterschiedlichen Trench-Geometrien

Die unterschiedlichen Geometrievarianten wurden auf einer Maske platziert. Am Lithographie-Stepper wurde dann jeweils nur ein Typ für die Belichtung ausgewählt. Im sogenannten Schachbrettentwurf handelt es sich nach wie vor um ein Streifen-Layout, jedoch ist jede zweite Struktur um 90 Grad gedreht. Diese Anordnungen, wie auch die rechteckigen Ringstrukturen und die Kreisstrukturen, haben die Zielsetzung, durch eine gleichmäßige Verteilung der Gräben in X- und Y-Richtung eine Stresskompensation zu erreichen.

#### 1.3.3 Redesign

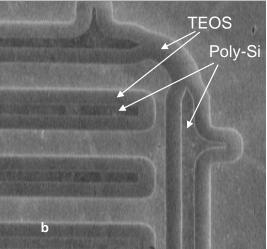

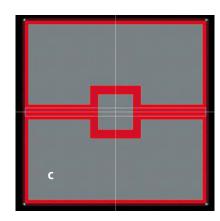

Die Ergebnisse der Stressanalyse unterschiedlicher Trench-Geometrien wie Streifen-, quadratische- und kreisförmige Designs, haben die Notwendigkeit aufgezeigt, im Redesign die Orientierung der tiefen Gräben in X- und Y- Richtung gleichmäßig verteilt auszulegen. Dies ist bei den quadratischen (Square-Racetrack) und kreisförmigen (Circle-Racetrack) Designs gegeben, wohingegen bei den Streifen-Designs, gemäß Abb. 1.7, jedes zweite Bauelement um 90° gedreht platziert wurde (Checkerboard).

Abb. 1.7: Redesign: Maskenlayout der Feldplatten-Kompensationsbauelemente

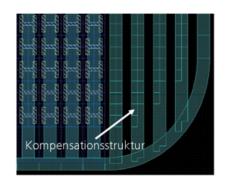

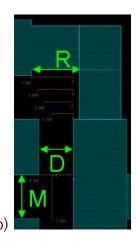

Des Weiteren wurde im Masken-Redesign eine Verbesserung der Kompensationsstrukturen für eine 3D-Kompensation im Rand- bzw. Eckenbereich der Bauelemente vorgenommen, um eine Über- bzw. Unterkompensation zu vermeiden.

In einem ersten Ansatz wurde die in der Abb. 1.8 b dargestellte Konstruktion gewählt, die im Eckenbereich keine Feldplatte mehr besitzt und deren Kompensation durch entsprechende Wahl der Geometrieparameter Mesabreite M, Ecken-Parameter R und Abstand D eingestellt wird.

Abb. 1.8 a) Erster Redesign: Streifenlayout mit Center-Gate und vertikalem Gatefinger b) Ausschnitt: Feldplatten-Trench-Geometrie der äußeren Ecken für 3-dimensionale Ladungskompensation

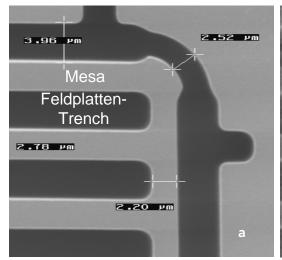

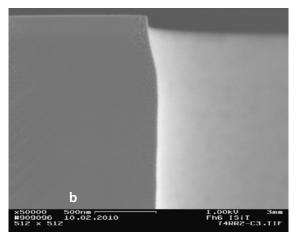

Abb. 1.9: Zweiter Redesign mit abgerundeten Ecken,

- a) SEM-Bild nach Feldplatten-Trench-Ätzung

- b) SEM-Bild gefüllter Trench mit TEOS-Oxid und Poly-Silizium Feldplatte

Diese Ecken-Konstruktion der Kompensationsstruktur wurde in einem zweiten Redesign durch eine Verrundung weiter optimiert. Die Abb. 1.9 zeigt die Draufsicht einer ladungskompensierten Ecke eines Streifenlayouts. Durch Verringerung der Trenchbreite im Krümmungsbereich der Ecke wird der Trench bereits durch die Deposition des Isolationsoxids geschlossen, wodurch die weitere Abscheidung der Poly-Si Feldplatte in diesem Bereich verhindert wird. Die für den Eckenbereich typische Überkompensation, die bestimmend für die Durchbruchsspannung ist, wird dadurch unterbunden. Durch Optimierung der geeigneten Parameter R, M und D wird der Kompensationpunkt eingestellt.

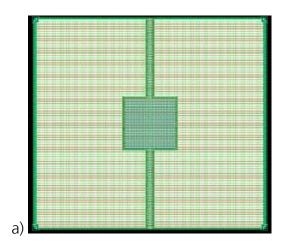

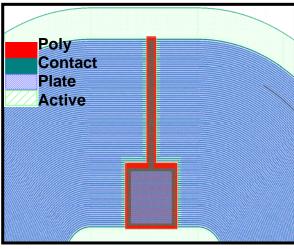

Als Referenzbauelement mit idealer Kompensation wurde das Circle-Design gewählt, dass aufgrund seiner Winkelsymmetrie homogene Bedingungen für die Ladungskompensation bietet.

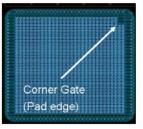

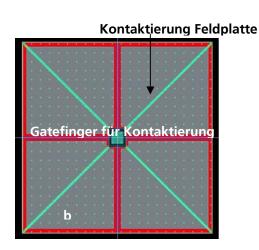

Abb. 1.10 a) Circle Layout gesamt sowie Ausschnitt aus dem Mittenbereich (Gate-Pad) b) Square Racetrack Layout gesamt sowie Ausschnitt aus dem Mittenbereich (Gate-Pad)

Die Gesamtansicht für das Circle- und Square-Racetrack-Design, sowie deren jeweilige Detailbilder des Mittenbereichs für den Gate-Anschluss, sind in den Abb. 1.10 a und b dargestellt. Für das Square-Racetrack-Design wurde keine 3D-Eckenkompensation vorgenommen, um einen Vergleich mit der idealen Circle-Struktur durchführen zu können. Weitere Ausführungen zur Kompensation des Square-Racetrack Layouts werden im nachfolgenden Split-Gate Kapitel diskutiert.

## 1.4 Herstellungstechnologie von Kompensationsdioden und Transistoren

#### 1.4.1 Wafer-Substrat und Epitaxie Spezifikation

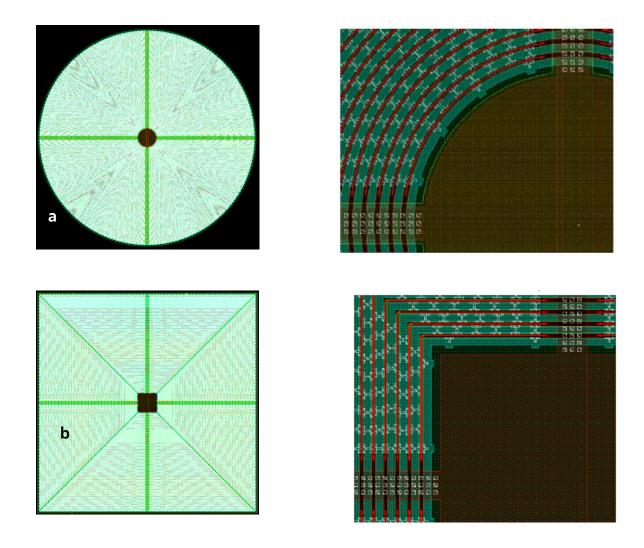

Die Technologieentwicklung für Feldplatten-Kompensationsbauelemente wurde zunächst auf 6 Zoll Wafer durchgeführt, aber bereits nach wenigen Chargendurchläufen auf 8 Zoll umgestellt. Basierend auf den Ergebnissen von Simulationen wurden für die epitaktische Driftzone zweistufige- und dreistufige Schichtfolgen festgelegt (Tab.1.3), um den besten Kompromiss hinsichtlich optimaler Verarmung bei höchstmöglicher Dotierungskonzentration zu finden.

Tab. 1.3: Substrat- und Epitaxie-Spezifikationen 6" Wafer

Die Spezifikation der 2-Step-Epitaxie wurde bei der Umstellung auf 8 Zoll Wafer nicht geändert. Im letzten Projektabschnitt wurde außerdem ein angepasster 3 Step-Epitaxie Aufbau für 12 µm tiefe Trenches eingesetzt (Tab.1.4).

Tab. 1.4: Substrat- und Epitaxie-Spezifikationen 8" Wafer

| 2-Step Epitaxie (17µm)                                                                                                                                   | 3-Step Epitaxie (20µm)                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Substrat 8" 725 μm As: 5,0 E19 cm <sup>-3</sup><br>Epi-Layer 1 10,5 μm, Ph: 1,5 E16 cm <sup>-3</sup><br>Epi-Layer 2 6,5 μm, Ph: 5,5 E15 cm <sup>-3</sup> | Substrat 8" 725 μm As: 5,0 E19 cm <sup>-3</sup><br>Epi-Layer 1 9,0 μm, Ph: 1,1 E15 cm <sup>-3</sup><br>Epi-Layer 2 4,5 μm, Ph: 9,0 E15 cm <sup>-3</sup><br>Epi-Layer 3 6,5 μm, Ph: 8,0 E15 cm <sup>-3</sup> |

#### 1.4.2 Stressuntersuchungen

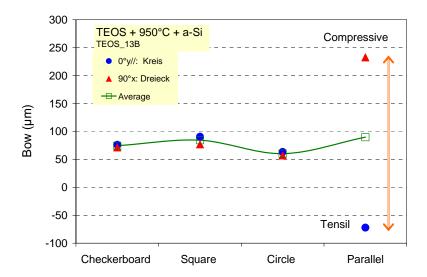

Die Ergebnisse des ersten Technologie-Durchlaufs zeigten eine erhebliche Verbiegung der Wafer infolge der mechanischen Spannung der parallel laufenden bis zu 20µm tiefen Feldplattenstrukturen. Zum Einen erschwert eine starke Verbiegung der Wafer die weitere Prozessierung, zum Anderen hat der mechanische Stress im Bauelement erhöhte Leckströme zur Folge. Ziel der Stressuntersuchungen war es, den Einfluß von unterschiedlichen Trench-Geometrien (Testmaske mit Schachbrett-, rechteckige Ringstruktur-, kreisförmige Ringstruktur- und paralleler- Anordnung) zu untersuchen. Die Ergebnisse für den Wafer-Bow in Abhängigkeit von der gewählten Geometrie werden in der Abb. 1.11 gezeigt. Dargestellt ist die Waferverbiegung in x- und y-Richtung von SiO<sub>2</sub> und Poly-Si gefüllten Kompensationsstrukturen vor der Planarisierung durch CMP .

Abb 1.11: Mechanische Durchbiegung (Bow) in Abhängigkeit von der Grabengeometrie

Die parallele Anordnung der Gräben zeigt erwartungsgemäß einen großen Wafer-Bow, der in x- und y-Richtung infolge von Zug- und Druckspannung unterschiedliche Werte annimmt. Alle alternativen Geometrien hingegen weisen vor dem CMP-Prozess einen Wafer-Bow unter 100 µm auf. In vorausgegangenen Experimenten wurde festgestellt, dass der nachfolgende CMP-Prozess aufgrund seines lateralen Materialabtrags die Durchbiegung weiter verringert. Die Versuche haben außerdem gezeigt, dass Hochtemperaturschritte (>950°C) nach dem Füllen der Feldplattengräben vermieden werden müssen. Die positiven Ergebnisse aus dem Geometrie-Variations-Experiment wurden bei dem Redesign des Maskensatzes berücksichtigt.

#### 1.4.3 Herstellungsprozess

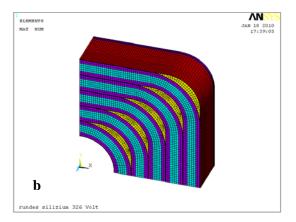

Der Herstellungsprozess für Dual-Gate-Bauelemente wurde in mehreren Technologiedurchläufen, sowohl für Transistoren als auch für Dioden mit Kompensationsfeldplatte, optimiert (Abb.1.12). Ausgehend von Si-Substraten mit mehrstufigen Epitaxie-Schichten wurden zunächst die p-Body-Gebiete erzeugt. Durch diese Maßnahme wird der Hochtemperaturschritt für die p-Body-Diffusion nach der Herstellung der Feldplatten in den tiefen Trenchstrukturen vermieden, was zu einer signifikanten Reduzierung der Stressentwicklung führt.

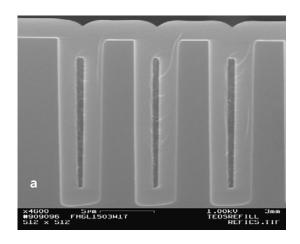

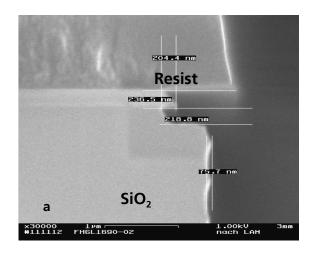

Es ist die Zielsetzung der Trench-Ätzung für die Kompensationsstruktur, neben der festgelegten Trenchtiefe, einen geringen aber positiven "Slope" der Trenchwände, mit einer möglichst geringen Seitenwandrauhigkeit, zu erreichen (Abb.1.12a). Das Trenchprofil wird durch einen zusätzlichen isotropen Ätzschritt (Roundhole), sowie einer Oxidation mit nachfolgender naßchemischer Oxidätzung, geglättet. Diese Prozessschritte bewirken einen lateralen Kantenverlust, der durch einen entsprechenden Vorhalt im Maskendesign berücksichtigt werden muss. Die Breite des Feldplattentrench beträgt an der Siliziumoberfläche je nach verwendeter Ätzanlage und Prozessführung 3,8 μm bis 4,2 μm.

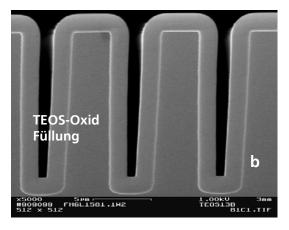

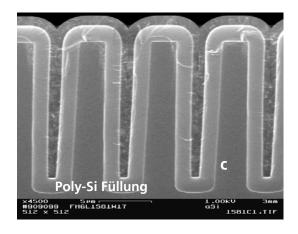

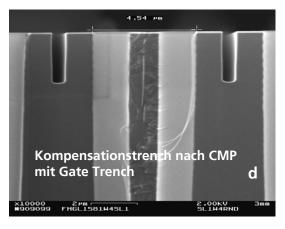

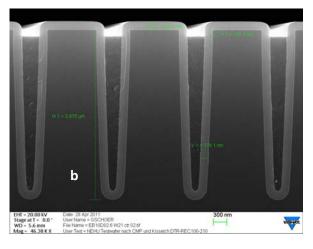

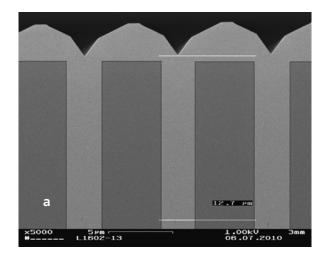

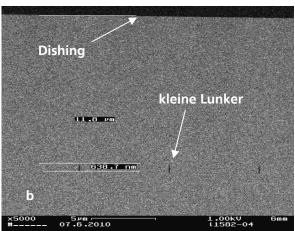

Abb. 1.12: SEM Bilder zur Beschreibung des SuperPowerMOS Herstellungsprozesses a) nach Trench-Ätzung, b) nach TEOS-Oxid Deposition, c) nach Poly-Si Füllung, d) nach CMP und Gate Trench-Ätzung

Die Gräben werden mit TEOS Isolationsoxid und mit dotiertem amorphen Silizium gefüllt (Abb.1.12 b,c). Das optimierte Trenchprofil ermöglicht eine nahezu vollständige Füllung der Trenches ohne Lunkerbildung, wobei eine hochkonforme Teos-Deposition erforderlich ist. Zur Vorbereitung des eigentlichen Transistor-Moduls wird die Oberfläche des Wafers durch chemisch-mechanisches Polieren (CMP) in zwei Schritten planarisiert, ohne die Oberfläche zu schädigen. Zunächst wird die Poly-Silizium Schicht mittels CMP zurückpoliert, anschließend wird das Isolationsoxid teilweise nasschemisch zurückgeätzt, um dann das restliche Oxid in einem zweiten CMP-Schritt zu entfernen. Der Gate-Trench des PowerMOS-Transistors wird in die Mitte des Mesabereichs zwischen den Feldplatten plaziert. Die Prozessierung des Gate-Moduls erfolgt im wesentlichen gemäß der Standard-Prozessseguenz mit Gate-Oxid und POCL3-dotiertem Poly-Silizium. Im Hinblick auf das Anwachsen des mechanischen Stress, ist auf kleinstmögliches thermisches Budget zu achten. Hier zeigt sich, dass infolge der Fehlanpassung der thermischen Ausdehnungskoeffizienten zwischen der Poly-Si Feldplatte und dem Isolationsoxid, insbesondere bei tiefen Trenchstrukturen und dicken Oxidschichten, eine erhebliche lokale mechanische Spannung auftreten kann, die u.U. zur Kristallschädigung innerhalb der Mesa Gebiete

Die weiteren Prozesse für die Fertigstellung der Bauelemente folgen weitgehend der Standard-PowerMOS-Technologie. Die Kontaktierung der p-Body- und Source-Gebiete des Transistors sowie der Kompensationsfeldplatte erfolgt durch H-förmige Kontaktlochstrukturen, die durch die AlCu-Metallisierung miteinander verbunden werden.

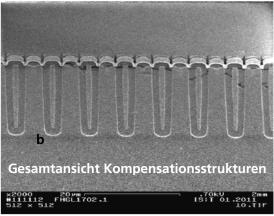

Abb.1.13: SEM-Darstellung eines fertig gestellten Dual-Gate PowerMOS-Transistors

- a) SEM-Darstellung Transistorzelle

- b) SEM-Darstellung Gesamtansicht mehrerer Kompensationszellen

Der Fertigungsprozess schließt ab mit dem Dünnschleifen der Wafer und der rückseitigen Metallisierung. Die Abb. 1.13 zeigt ein typisches SEM Schnittbild eines Dual-Gate Kompensationsbauelementes im Detail sowie in Gesamtansicht.

## 1.5 Elektrische Charakterisierung

Die elektrische Charakterisierung von Leistungsbauelementen mit vertikalen Feldplatten erfolgte zuerst an Diodenstrukturen und anschließend an Transistoren. Aus der Dioden-Kennlinie im Durchlass- und Sperrbereich lassen sich wichtige Kenngrößen extrahieren, die auch auf einen baugleichen Transistor übertragbar sind. So werden der Einfluss der Feldplattenkompensation auf die Durchbruchspannung sowie das Leckstromverhalten ermittelt.

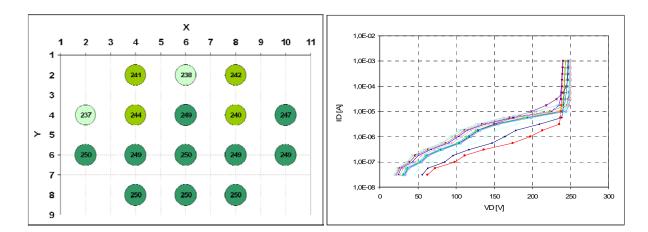

Abb. 1.14: Verteilung der Durchbruchspannung eines Circle-Design Bauelements über einen 8 Zoll-Wafer mit dazugehörigen Sperrkennlinien

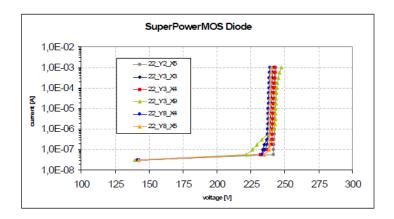

An feldplattenkompensierten Dioden mit kreisförmigen Trenchstrukturen (Circle Design) wurden Durchbruchspannungen bis 250 V gemessen, die nur bei optimaler Kompensation der Bauelemente durch die Feldplatten erreicht werden kann. Der Referenzwert eines planaren p-n-Übergangs bei gleicher Dotierungskonzentration

(1x10<sup>16</sup>cm<sup>-2</sup>) liegt bei ca. 70V. Die Verteilung der Messergebnisse für die Durchbruchspannungen über einen 8-Zoll Wafer wird in Abb.1.14 dargestellt. Mehr als 85% der Bauelemente des Circle Designs liegen in der Durchbruchspannung oberhalb der Spezifikationsgrenze von 240V. Vergleichbare Werte werden an Bauelementen gemessen, die ein eckenkompensiertes Streifenlayout aufweisen. Die Sperrcharakteristik am Beispiel des Circle-Design Bauelements hat gezeigt, dass der Leckstrom durch Verbesserungen im Maskenlayout und durch eine optimierte Prozessführung deutlich reduziert werden konnte. Beste Kurvenverläufe der Sperrcharakteristik mit Leckströmen <50nA sind in der Abb.1.15 dargestellt. Trotz dieser positiven Einzelergebnisse bleibt für tiefe Trenchstrukturen und dicken Isolationoxiden dass Risiko erhöhter Leckströme bestehen

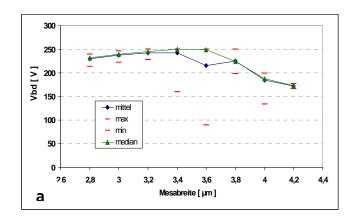

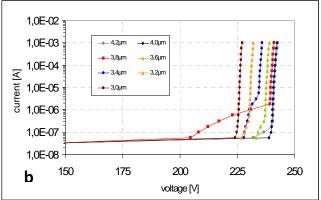

Die Darstellung 1.16 a zeigt den Verlauf der Kompensationskurve als Abhängigkeit der Durchbruchspannung von der Mesa-Breite. Das Maximum der Kurve ist relativ breit ausgeprägt, bei einer optimalen Durchbruchspannung von ca. 250V. In Richtung größerer Mesa-Breiten, d.h. bei Unterkompensation, ist eine stärkere Reduktion der Sperrspannung festzustellen, als im Bereich der Überkompensation. Die Abb. 1.16 b zeigt die zur Kompensationskurve zugehörigen typischen Sperrstromverläufe.

Abb. 1.15: Sperrcharakteristik mit Leckstromwerten < 50nA für Circle-Design Bauelemente

Abb. 1.16: a) Kompensationkurve Circle Layout: Abhängigkeit der Durchbruchspannung von der Mesabreite b) Sperrcharakteristika für unterschiedliche Mesabreiten (3,0µm-4,2µm) gemäß Kompensationskurve

Die Optimierung des R<sub>Dson</sub> für Feldplatten Kompensationsbauelemente einer bestimmten Spannungsklasse ist abhängig von der Auslegung der epitaktischen Schicht. Hierfür gibt es prinzipiell 2 Ansätze:

- 1. Die Driftzone ist derart bemessen, dass der Kompensationstrench in etwa der Tiefe der epitaktischen Schicht entspricht. Somit ist die Driftzone auch gleichzeitig der Kompensationbereich. Für die Reduzierung der kritischen Feldstärke im Sperrfall an der unteren Trenchkante und am pn-Übergang werden sowohl ein dickes Isolationsoxid als auch eine größere Trenchtiefe benötigt. Der Vorteil besteht in der Erreichbarkeit eines minimalen R<sub>DSon</sub>, der Nachteil besteht im technologischen Risiko, da tiefe Trenches und dicke SiO<sub>2</sub>-Schichten zu erheblicher mechanischer Spannung führen.

- 2. Die Driftzone ist derart bemessen, dass der Kompensationstrench flacher als die epitaktische Schichtdicke ist. In diesem Fall existiert unterhalb des Trenches eine zusätzliche Driftzone, die nicht zum Kompensationsbereich gehört. Diese Driftzone reduziert im Sperrfall die Feldstärke, sodass flachere Gräben und geringere SiO<sub>2</sub>-Schichten für die jeweilige Spannungsfestigkeit ausreichen. Der Nachteil besteht diesmal in dem höheren R<sub>DSon</sub>, Wert, der Vorteil ergibt sich aus dem geringeren technologischen Risiko. Im Rahmen des Projektes wurden beide Varianten untersucht.

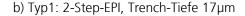

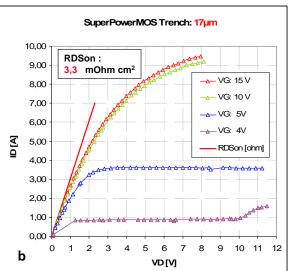

Zielsetzung von Transistor Typ 1 war die Reduzierung des  $R_{DSon}$  auf ein Minimum bei Einhaltung einer Durchbruchspannung von 250V. Verwendet wurde eine zweistufige Epitaxie (Epi-Layer 1 :10,5 µm, Ph: 1,5  $10^{16}$  cm<sup>-3</sup>, Epi-Layer 2: 6,5 µm, Ph: 5,5  $10^{15}$  cm<sup>-3</sup>) mit 17µm tiefen Feldplattengräben. Die Abbildung 1.17.b zeigt das zugehörige Ausgangskennlinienfeld mit einem sehr geringen spezifischen  $R_{DSon}$  von 3,3 mOhmcm<sup>2</sup>.

Der Herstellungsprozess von Transistor-Typ 2 wurde angepasst, um eine Durchbruchspannung zu erreichen, die mindestens 10% über dem Nennwert liegt, also bei  $V_{bd}$ =275V. Außerdem sollte gezeigt werden, dass mit reduzierter Trenchtiefe und verringerter Oxid-Dicke der Drain-Leckstrom minimiert werden kann. Für diesen Ansatz wurde eine angepasste dreistufige Epitaxie (Layer 1: 9,0 µm, Ph: 1,1  $10^{15}$  cm<sup>-3</sup>, Layer 2: 4,5 µm, Ph: 9,0  $10^{15}$  cm<sup>-3</sup>, Layer 3: 6,5 µm, Ph: 8,0  $10^{15}$  cm<sup>-3</sup>) mit 12µm tiefen Feldplattengräben gewählt. Unter diesen technologischen Randbedingungen konnte ein spezifischer  $R_{DSon}$  von 5,4 mOhmcm<sup>2</sup> erreicht werden (Abb. 1.17.a).

a) Typ2: 3-Step EPI, Trench-Tiefe 12µm

Abb. 1.17 Ausgangskennlinienfeld von Dual Gate Kompensationsbauelementen

- a) Ausgangskennlinienfeld Typ 2 mit 12µm tiefen Trenches

- b) Ausgangskennlinienfeld Typ 1 mit 17µm tiefen Trenches

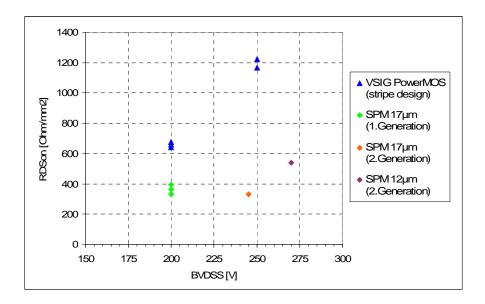

Abb. 1.18 Vergleich des spezifischen On-Widerstands R<sub>DSon</sub> und der Durchbruchspannung von Standard-PowerMOS- mit SuperPowerMOS-Transistoren (Feldplatten-Kompensation)

Die im Rahmen dieses Projektes hergestellten Dual-Gate PowerMOS-Bauelemente auf Basis einer Feldplatten-Kompensation zeigen in der 200 V Spannungsklasse im Vergleich zu herkömmlichen PowerMOS-Bauelementen (Abb. 1.18) eine Verbesserung des On-Widerstands um den Faktor 2. In der 250V-Spannungsklasse wurde sogar eine Verbesserung des  $R_{DSon}$  um den Faktor 3 erreicht.

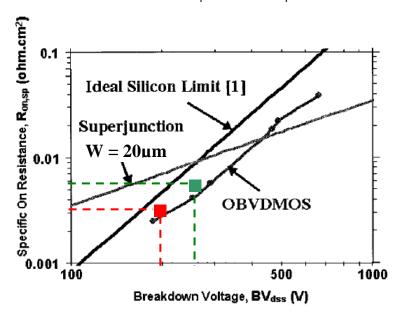

In der Abb. 1.19 sind die erreichten R<sub>DSon</sub> Werte in die im Antrag gezeigte theoretische Trade-Off Kurve eingezeichnet. Die Werte stehen in guter Übereinstimmung mit den simulierten Werten für die Feldplatten-Kompensationsbauelemente (OBVDMOS).

[1] [Yung C. Liang et. al., Oxide-Bypassed VDMOS: An alternative to Superjunction High-Voltage-PowerMOS devices, IEEE Electron Device Letters, Vol.22, August 2001, pp. 407-409)

Abb. 1.19 Abhängigkeit des spezifischen On-Widerstands von der Durchbruchsspannung für Super-Junction- CoolMOS, Super-PowerMOS (OBVDMOS) sowie dem idealen Driftzonen Widerstand (Si-Limit)

## 1.6 Zusammenfassung

Im Rahmen des Projekts wurden neue Architekturansätze für feldplattenbasierte Kompensationsbauelemente für den Spannungsbereich bis 250V untersucht. Hierbei wurden 3 verschiedene Layout-Typen, Streifen, Circle- und Square–Racetrack, betrachtet und hinsichtlich ihrer Kompensationseigenschaften erprobt. Umfängliche Variationen des Bauelementedesign wurden im Hinblick auf die Optimierung der Ladungskompensation auf zwei unterschiedlichen Maskensätzen umgesetzt, wobei die 3D-Randkompensation eine besondere Bedeutung hatte.

Für die technologische Realisierung der Bauelemente mussten neue Prozesse wie das Hochratenätzen tiefer Trenchstrukturen, deren konforme Auffüllung mit SiO₂ und Poly-Si sowie chemisch-mechanisches Polieren (CMP) bereitgestellt und in den Gesamtprozess integriert werden.

Als besondere Herausforderung haben sich erhöhte Leckströmen erwiesen, die infolge der Entstehung von Generationszentren entlang der Kompensationsstrukturen, durch Ätzdefekte und Fehlanpassung thermischer Ausdehnungskoeffizienten, ein zentrales F&E Thema waren. Insbesondere musste zur Reduzierung der mechanischen Spannung im Hinblick auf den Gesamtprozess eine stressoptimierte Technologie berücksichtigt werden. Ein neuer Trade-Off zwischen R<sub>DSon</sub> und der technologischen Beherrschbarkeit thermomechanischer Randbedingungen musste in Betracht gezogen werden. Dies betrifft die Festlegung von Layout, Schichtdicken und Trenchtiefen sowie Fragestellungen der Prozessintegration zur Erreichung des kleinstmöglichen Einschaltwiderstands.

Der spezifische On-Widerstand konnte für die 250V Spannungsklasse im Vergleich zu herkömmlichen PowerMOS-Transistoren um den Faktor 3 reduziert werden, was weitgehend in Übereinstimmung mit theoretischen Betrachtungen steht.

Die elektrischen Ergebnisse der unterschiedlichen Design-Typen mit großer Variation von Geometrie-Parametern sind Ausgangspunkt für die Auswahl von geeigneten Kompensationsbauelementen für einen neuen produktionstauglichen Maskensatz zur Herstellung erster Prototypen.

Die gemeinsam mit Vishay durchgeführten F&E Arbeiten haben die Voraussetzung geschaffen, feldplattenbasierte Kompensationsbauelemente der 250V Spannungsklasse schnellstmöglich in die Produktion zu überführen.

## 2. Split-Gate Bauelemente

## 2.1 Einleitung

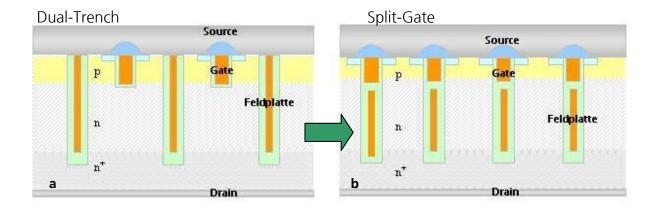

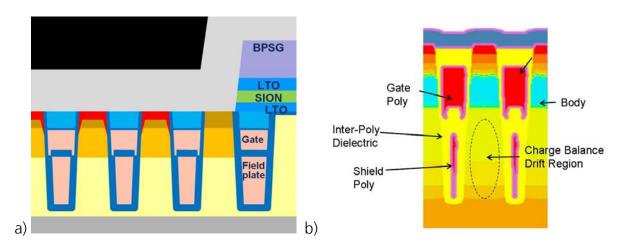

Der Split-Gate PowerMOS Transistor stellt die nächste Entwicklungsstufe des Dual-Trench Transistors dar, mit der Zielsetzung der weiteren Reduzierung des Einschaltwiderstands R<sub>DSon</sub>. Daher vereint der Split-Gate Ansatz die für die Ladungskompensation erforderliche Feldplatte mit dem PowerMOS Transistor in derselben Trenchstruktur, dargestellt in der Abb. 2.1b.

Im Gegensatz zum Dual-Trench Ansatz befindet sich der PowerMOS Transistor beim sogenannten Split-Gate Prinzip direkt oberhalb der Kompensationsfeldplatte. Der Vorteil dieser Technologie besteht in der Erhöhung der Trenchdichte mit besserer Nutzung der aktiven Fläche, d.h. es wird eine größere effektive Kanalweite des Bauelementes erreicht. Durch die mögliche Verringerung der Mesabreite (Abstand zwischen den Trenchstrukturen) kann gemäß der Kompensationsbedingung die Driftzonendotierungskonzentration zusätzlich erhöht werden. Je nach Auslegung des Bauelements können beide Maßnahmen zu einer weiteren Reduzierung des Einschaltwiderstands bis ca. Faktor 2 genutzt werden.

Abb. 2.1 Prinzipdarstellung einer a) Dual-Trench- und b) Split-Gate-Struktur im Vergleich

Die Platzierung des Transistors direkt auf der Feldplatte erfordert jedoch einen komplett neuen Prozessablauf mit einem speziellen Maskendesign. Zur technologischen Verifikation des Split-Gate Ansatzes wurde ein erster Technologiedemonstrator mit tiefen Trenchstrukturen bis ca. 17µm hergestellt, geeignet für Spannungen bis ca. 300V.

Die Untersuchungen haben jedoch erhebliche mechanische Stresseffekte bedingt durch die thermische Fehlanpassung der Poly-Si/SiO<sub>2</sub> Schichtenfolge der Feldplatten-Kompensationsstruktur gezeigt, die bereits bei Dual-Gate Bauelementen Gegenstand intensiver F&E Betrachtungen waren.

Aufbauend auf diesen Ergebnissen wurden für die Bauelemente- und Designverifikation daher Trenchstrukturen mit einer Tiefe <5µm gewählt, um eine technologische Basis für den Spannungsbereich 50-100V zu evaluieren. Diese Vorgehensweise gestattet die zukünftige sukzessive Weiterentwicklung in Richtung höherer Spannungen und steht in Übereinstimmung mit den Marktanforderungen und der Entwicklungs-Roadmap.

## 2.2 Simulation und Bauelemente-Design

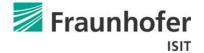

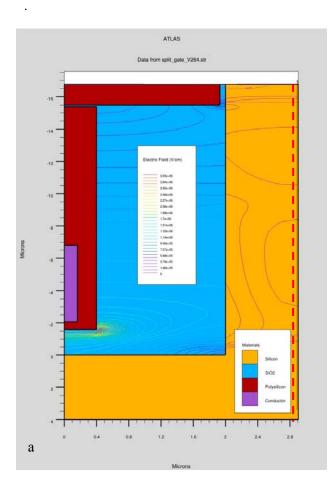

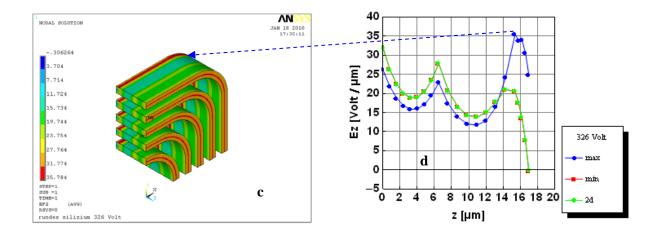

Wie für die Dual-Gate Struktur wurden auch für die Split-Gate Zelle zunächst 2D-Simulationen unter vergleichbaren geometrischen Randbedingungen durchgeführt. Die Abb. 2.2 zeigt eine Split-Gate Zelle mit einer Trenchtiefe von ca.17µm und einer Oxiddicke von 1,6µm. Die zweistufige Dotierung der Driftzone sowie die Mesabreite wurden im Kompensationsfall für den Spannungsbereich von 250 V ausgelegt. Der vertikale Feldstärkeverlauf in der Mesamitte zeigt eine typische Charakteristik mit ausgeprägten Maxima an den Stellen starker Dotierungsänderung. Die größte Feldstärke tritt erwartungsgemäß am oberen p-Body p-n-Übergang auf. Bei Betrachtung der Feldstärke entlang der Trenchkante wäre das Maximum an der unteren Trenchkante zu erwarten. Die Simulation des R<sub>DSon</sub> ergab für eine Mesabreite von 1,8µm, d.h. bei einer Erhöhung der Zelldichte von ca. 25%, einen Wert von 1,8 mOhmcm<sup>2</sup>. Der Vergleichswert für die Dual Gate Struktur wurde mit 2,5 mOhmcm² bestimmt, woraus eine Reduzierung des R<sub>DSon</sub> von ca.30% resultiert. Eine weitere Verringerung des R<sub>DSon</sub> ließe sich erreichen durch Erhöhung der Zelldichte, verbunden mit einer Anhebung der Driftzonendotierung. Es sei darauf hingewiesen, dass bei steigendem technologischen Risiko durch aggressive Bauelementeskalierung eine Kosten – Nutzen Abwägung erforderlich ist.

Abb. 2.2 a) Simulation der elektrischen Feldstärke einer PowerMOS Split-Gate Zelle für den Spannungsbereich 250V;

b) vertikaler Feldstärkeverlauf in der Mitte der Si-Mesa-Struktur (rechter Bildrand a) rote Linie)

Basierend auf den Designerfahrungen der Dual-Trench Bauelemente wurde ein Split-Gate Konzept erarbeitet und in erste Layoutvarianten übertragen.

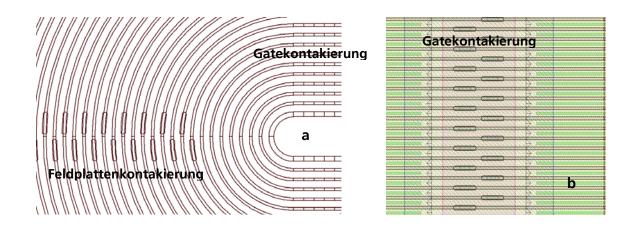

Die Abbildung 2.3 zeigt die prinzipiellen Designansätze Circle- (a), Racetrack- (b) und Stripe-Design (c) für die Split-Gate Devices, wobei insbesondere die Eckenkompensationen im Hinblick auf die maximalen Feldstärken von Interesse waren.

Abb. 2.3 a) Circle-, b) Racetrack- und c) Stripe-Design

Im Gegensatz zum Circle-Design erfordern Racetrack- und Streifen-Layouts eine Ladungskompensation in den Eckenbereichen. Die Ladungskompensation des Streifen-Designs wurde für die Dual-Gate Bauelemente bereits vorgestellt.

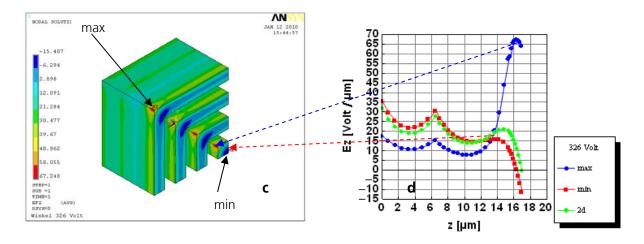

Da für den Racetrack Ansatz eine 3D-Kompensationen im Rand- und Eckenbereich für Dual-Gate Bauelemente bisher nicht berücksichtigt war, wurde mittels FEM-Simulation ein erster 3D-Kompensationsansatz erarbeitet. Abb. 2.4 a und b zeigen die Draufsicht sowie die 3D-Darstellung der simulierten Racetrack Struktur ohne Eckenkompensation. Es ist anschaulich ersichtlich, dass im Eckenbereich die Bedingung vollständiger Ladungskompensation nicht erfüllt ist.

Abb. 2.4 a) 2D-Draufsicht einer Racetrack Struktur ohne Eckenkompensation b) 3D Ansicht einer Racetrack Struktur ohne Eckenkompensation

Abb. 2.4 c) 3D-FEM-Simulation einer Racetrack Mesa-Struktur ohne Eckenkompensation. Deutlich Erkennbar die Lokationen größter Feldstärke im unteren Eckenbereich der Mesastruktur durch Überkompensation(roter Bereich)

d) Vertikaler Verlauf der elektrischen Feldstärke entlang der Si-Mesakante grün: ungestörter kompensierter Bereich außerhalb der Ecken rot: unterkompensierter Bereich in den Mesa-Ecken (Abb. c dunkelblauer Bereich) blau: überkompensierter Bereich in den Mesa-Ecken (Abb. c roter Bereich)

Die 3-D-Verteilung der elektrischen Feldstärke in den Si-Mesa-Bereichen ist in der Abb. 2.4 c dargestellt, wobei die Feldplattenstrukturen ausgeblendet sind. Die Feldstärke-Maxima befinden sich erwartungsgemäß in den äußeren Ecken der unteren Mesa-Bereiche, die Minima dagegen in den inneren Ecken. Somit zeigen die blauen Bereiche unterkompensierte Gebiete der Si-Mesa-Strukturen, wohingegen die roten Gebiete mit maximaler Feldstärke überkompensiert sind.

Die im Eckenbereich unkompensierte Racetrack Struktur zeigt in der Simulation maximale Feldstärken bis zu 670 kV/cm, die signifikant oberhalb der kritischen Durchbruchsfeldstärke des Si liegen, wodurch die maximale Sperrspannung des Bauelementes nicht erreicht werden kann (blauer Pfeil). Dieser Effekt wurde bereits an Dual-Trench Bauelementen nachgewiesen.

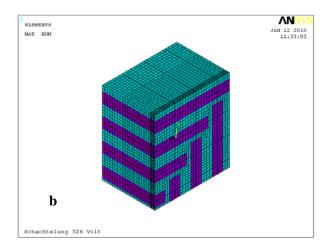

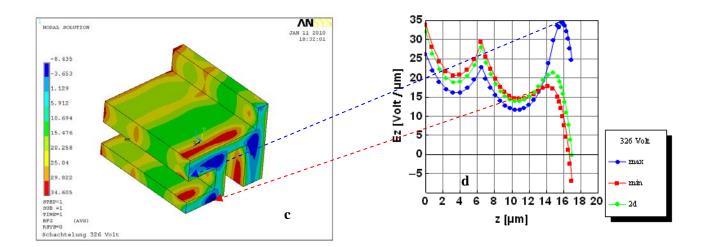

Ein erster Ansatz die Über- und Unterkompensation in den Racetrackecken zu reduzieren ist in der Abb. 2.5 gezeigt. Analog zur Abb. 2.4 werden in der Bildern a und b zunächst die 2D- und 3D Strukturgeometrien für eine Eckenkompensation gezeigt. Diese Konstruktion basiert im Eckenbereich auf einer "Verschachtelung" der ansonsten orthogonalen Feldplattentrenches. Für den Abstandsparameter D wurden in vertikalerwie auch horizontaler Richtung gleiche Werte gewählt. Die FEM-Simulationen zeigen, dass eine "geschachtelte" Mesa-Struktur die maximale Feldstärke in Abhängigkeit des Parameters D deutlich reduzieren kann. Das Optimum für die maximale Feldstärke wurde bei einem D-Wert von ca. 50% der Mesabreite (1,7μm) gefunden.

Abb. 2.5 a) 2D-Draufsicht einer Racetrack Struktur mit Eckenkompensation b) 3D Ansicht einer Racetrack Struktur mit Eckenkompensation

Abb. 2.5 c) 3D-FEM-Simulation einer Racetrack Mesa-Struktur mit Eckenkompensation. Deutlich Erkennbar die Lokationen größter Feldstärke im untern Eckenbereich der Mesastruktur (roter Bereich)

d) Vertikaler E-Feldstärkeverlauf entlang ausgewählter Bereiche der Si-Mesakante grün: ungestörter kompensierter Bereich außerhalb der Ecken (2D-Bereich) rot: Verlauf E-Feldstärke min entlang der Mesakante (Abb. c dunkelblauer Bereich) blau: Verlauf E-Feldstärke max entlang der Mesakante (Abb. c roter Bereich)

Der 3D-Feldstärkeverlauf in der Si-Mesa-Struktur ist in der Abb. 2.5 c dargestellt. Die maximale Feldstärke ist mit 350 kV/cm auf ca. den halben Wert gegenüber der unkompensierten Eckenstruktur reduziert. Das Maximum der Feldstärke tritt zwar noch im unteren Bereich der Trenchkante auf, ist aber nicht mehr in den Ecken lokalisiert.

Abb. 2.6 a) 2D-Draufsicht einer Racetrack Struktur mit idealer Eckenkompensation b) 3D Ansicht einer Racetrack Struktur mit idealer Eckenkompensation

Abb. 2.6 c) 3D-FEM-Simulation einer Racetrack Mesa-Struktur mit idealer Eckenkompensation. Deutlich Erkennbar die Lokationen größter Feldstärke im untern Eckenbereich der Mesastruktur (roter Bereich)

d) Vertikaler E-Feldstärkeverlauf entlang ausgewählter Bereiche der Si-Mesastruktur grün: ungestörter kompensierter Bereich außerhalb der Eckenrundungen (2D-Bereich) rot: Verlauf minimaler E-Feldstärke im Mesa-Volumen blau: Verlauf maximaler E-Feldstärke an der äußeren Mesakante (Abb. c roter Bereich)

Eine ideale Eckenstruktur ist in der Abb. 2.6 a,b dargestellt. Bei diesem Ansatz wird im Eckenbereich der Racetrack Struktur eine im Viertelkreis äquidistante Mesabreite  $d_{mesa}$  mit jeweils gleichem Innen- und Außenradius für alle Ringe des Bauelements gewählt. Diese Bedingung lässt sich nur erfüllen, wenn man eine veränderliche Trenchbreite für die Feldplatte in den gerundeten Ecken zulässt. Somit erhöht sich die maximale Trenchbreite auf der 45° Winkelhalbierenden auf den Wert  $d_{Trmin} = [(d_{Trmin} + d_{mesa}) \sqrt{2} - d_{mesa}]$ , wobei der  $d_{Trmin}$  die Trenchbreite auf den Geraden repräsentiert (3,5µm).

Bei einer gewählten Oxiddicke von 1,6µm und einer Poly-Si Feldplattendicke von 0,3µm im ungestörten Kompensationstrench müsste die Feldplatte in der Eckenrundung um mehr als Faktor 10 (ca. 3,15µm) zunehmen um eine ideale Kompensation zu erreichen. Ungeachtet der technologischen Herausforderungen bei der Realisierung der Kompensationstrenches mit zunehmender Feldplattenbreite sollen auch hier die Feldstärkebedingungen diskutiert werden.

Der vertikale Verlauf der maximalen elektrischen Feldstärke (roter Bereich, blaue Kurve) der Abb. 2.6 c, d zeigt im unteren Bereich der Mesakante Maximalwerte von ca. 350 kV/cm. Dieser Wert ist vergleichbar mit dem Maximalwert der "geschachtelten" Eckenvariante der Abb. 2.5, die mir einem D-Wert halber Mesabreite eine gute Approximation der idealen Eckenstruktur darstellt.

Der vertikale Verlauf der minimalen E-Feldstärke wurde in der Mitte der Mesastruktur aufgenommen und unterscheidet sich nicht vom 2D-Feldstäkeverlauf außerhalb des Eckenbereichs.

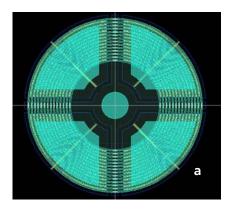

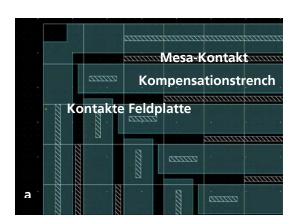

Ein Beispiel für ein "geschachteltes" Racetrack-Layout ist in der Abb.2.7 dargestellt. Für den Split-Gate Ansatz ist es erforderlich die im Trench unterhalb der Gate-Struktur befindliche Feldplatte separat zu kontaktieren. Die Feldplattenkontakte befinden sich auf den Chipdiagonalen und sind mit den Mesa-Bereichen (Source) verbunden. Die PowerMOS Transistorzellen, die sich oberhalb der Feldplatten befinden werden über orthogonale Gatefinger angeschlossen und zu einem Gatekontakt in der Chipmitte zusammengeführt.

Abb. 2.7 a) Ausschnitt des geschachtelten Racetrack-Layouts und b) Gesamtansicht de Racetrack Layouts mit Kontaktierung für Feldplatte und PowerMOS Gate

## 2.3 Herstellungstechnologie für Split Gate Bauelemente

#### 2.3.1 Herstellung eines Technologiedemonstrators

Die Zielsetzung für die erste Herstellung eines Technologiedemonstrators für die Spannungsklasse 250V war die frühzeitige Evaluierung der kritischen technologischen Schritte im Umgang mit tiefen Trenchstrukturen sowie dicker SiO<sub>2</sub>-Schichten in einem komplexen Gesamt-Prozessablauf.

Die Platzierung des Transistors direkt auf der Feldplatte bedingt einen neuen Technologieund Design-Ansatz. Zur Verifikation des Split-Gate Konzepts wurde zunächst ein erster Technologiedemonstrator auf Basis der Dual-Trench Layouts hergestellt.

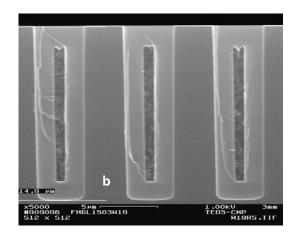

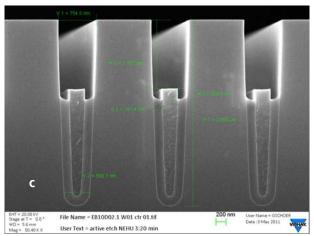

Der Prozessablauf folgt zunächst dem des Dual-Trench Ansatzes. Auch hier wird die Kompensationsstruktur zunächst durch Ätzen der ca. 17 $\mu$ m tiefen Si-Gräben sowie dem anschließenden Auffüllen mit 1,6 $\mu$ m SiO $_2$  und der für die Feldplatte erforderlichen Poly-Si Schicht hergestellt. Eine anschließende Planarisierung des Poly-Si mittels Chemisch-Mechanischem Polieren (CMP) ermöglicht die nachfolgende Rückätzung der Poly-Si Feldplatte.

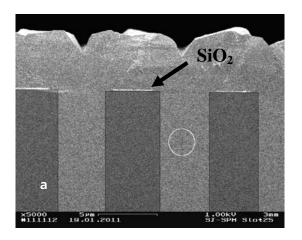

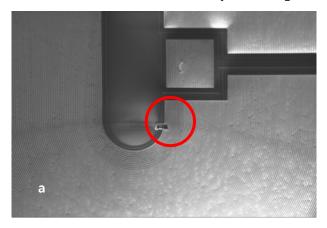

Nach dem Zurückätzen der Feldplatte wird der Trenchbereich oberhalb der Feldplatte erneut mit Oxid vollständig aufgefüllt und mittels CMP planarisiert. Die Abb. 2.8 a b zeigen SEM Bilder der Kompensationsstruktur mit bereits zurückgeätzter Feldplatte und darüberliegender SiO<sub>2</sub>-Auffüllung des Grabens vor und nach dem CMP-Prozess.

Das anschließende kontrollierte Zurückätzen des Oxides öffnet den oberen Trenchbereich für die Implementierung der Transistorstruktur. Hierbei wurden sowohl naßchemischesals auch Plasma-Ätzen erprobt, wobei die Gleichmäßigkeit des Ätzens ein wichtiges Kriterium darstellt. Für die Isolation oberhalb der Feldplatte wurde ein Restoxid von ca. 900nm vorgehalten.

Der freigelegte obere Trenchbereich steht somit zur Prozessierung der Gatestruktur zur Verfügung. Die weiteren Prozesse beinhalten die Voroxidation zur Beseitigung von oberflächenahen Si-Kristalldefekten sowie deren nachfolgende naßchemische SiO<sub>2</sub>-Ätzung. Die anschließende Gateoxidation mit nachfolgender Poly-Si Deposition und Dotierung sowie der Poly-Si Planarisierung mittels CMP schließen die Prozess-Sequenz für den Split-Gate Technologiedemonstrator ab.

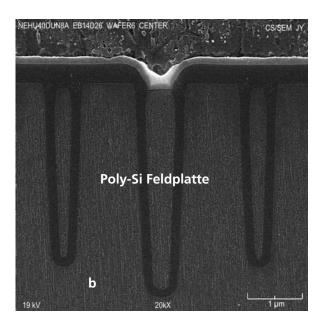

Die Abb. 2.8 c,d zeigen eine erste vollständig prozessierte Split-Gate Kompensationsstruktur mit einer Trenchtiefe von ca. 17µm.

#### Herstellung einer Split Gate Kompensationsstruktur

Abb. 2.8 a) SEM Darstellung einer Trenchstruktur mit zurückgeätzter Poly-Si Feldplatte und aufgefüllt mit TEOS-Oxid

- b) SEM Darstellung einer Trenchstruktur mit zurückgeätzter Poly-Si Feldplatte, aufgefüllt mit TEOS-Oxid und planarisiert mittels CMP

- c) SEM Darstellung von Split-Gate Zellen nach der Implementierung der Gatestruktur mit Gateoxid und planarisiertem Poly-Si

- d) Detaildarstellung der Gatestruktur oberhalb der isolierten Feldplatte

#### 2.3.2 Herstellung erster Split-Gate Bauelemente

Für die erste Verifikation des Technologie- und Designkonzepts wurden Split-Gate Bauelemente für den Spannungsbereich 50V ausgewählt um, basierend auf diesen Erfahrungen in einem nächsten Schritt die Skalierung für höhere Spannungen durchzuführen. Diese Vorgehensweise wurde gewählt, da das technologische Risiko für Bauelemente höherer Spannungsklassen erheblich ansteigt. Feldplatten-basierte Kompensationstrukturen benötigen für hohe Spannungen tiefe Si-Gräben, die mit dicken Isolationsoxiden und Poly-Si gefüllt werden müssen und je nach Design- und Technologiekonzept zu hohen mechanischen Spannungen führen können.

Basierend auf den Simulationen wurde für die Bauelementeherstellung eine Kombination aus Circle- und Racetrack-Layout gewählt, wobei die Kompensationsstrukturen ringförmig aufgebaut sind, mit halbkreisförmigen Verläufen im Krümmungsbereich des Bauelements. Der prinzipielle Verlauf der Trenchstrukuren ist in der Abb. 2.9 dargestellt.

Abb. 2.9 a) Darstellung der Layoutstruktur für ein Split-Gate Device basierend auf Racetrack mit Halbkreisen im Krümmungsbereich sowie Feldplatten- und Gatekontaktierung b) Darstellung der Gatekontaktierung in vertikaler Richtung

Das prinzipielle Technologiekonzept für die Herstellung des Split-Gate Bauelements ist in der Abb. 2.10 a dargestellt. Im Gegensatz zum Dual-Trench Ansatz wird für eine Zelle nur ein Si-Trench erzeugt. Der Gate-Bereich liegt oberhalb der Feldplatte, wodurch der Zellpitch und somit auch der R<sub>DSon</sub> reduziert werden kann. Zur Ermittlung der Geometrie und der Dotierungsprofile für eine optimale Feldplatten-Kompensation wurden Simulationen durchgeführt. Die Abb. 2.10 b zeigt einen Ausschnitt des Querschnitts einer simulierten Split-Gate Struktur. Dargestellt sind die Bereiche Gate-Poly, Feldplatten Poly-Si, das Inter-Poly-Dielektrikum sowie die p-Body- und Source-Gebiete und das kompensierte Driftzonen-Gebiet.

Abb. 2.10 a) Schematische Querschnittsdarstellung des Split-Gate Transistors b) Simulation der Split-Gate Struktur

#### <u>Herstellungstechnologie</u>

Wie alle n-Kanal PowerMOS Transistoren, so werden auch die Split-Gate Bauelemente auf ultrahochdotierten n<sup>++</sup> -Substraten hergestellt. Auf den Si-Substraten wird eine 2-stufige n-dotierte epitaktische Si-Schicht aufgewachsen. Die Schichtdicke und die Dotierung dieser Driftzonenschicht werden für die jeweilige Spannungsklasse und die Zellgeometrie angepasst. Die epitaktische Schichtdicke entspricht mindestens der Trenchtiefe für die Kompensationsstrukuren, wobei der obere Bereich etwas schwächer dotiert ist als der untere Bereich, um im Sperrbetrieb des Bauelements eine vollständige Verarmung der Driftzone zu gewährleisten.

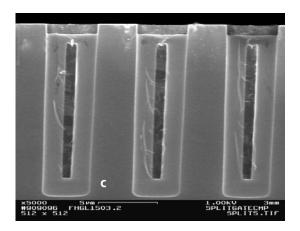

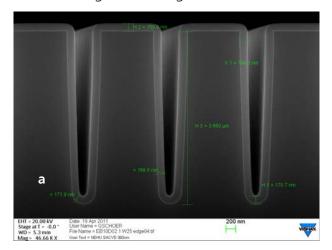

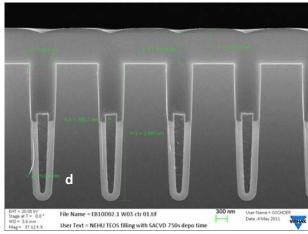

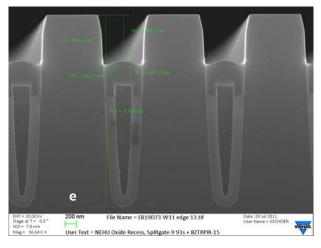

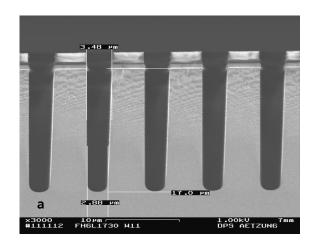

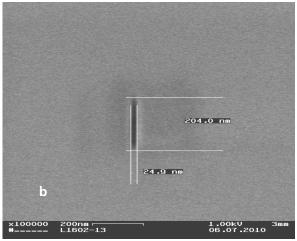

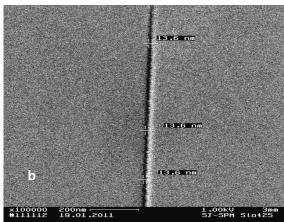

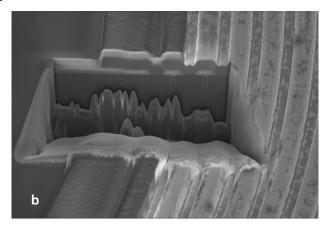

Die größte technologische Herausforderung beim Split-Gate Ansatz ist die Herstellung von geeigneten Trench-Strukturen, die hinsichtlich der Rauhigkeit der Seitenwände sowie der Trenchprofile optimiert werden müssen. Nach der Trenchätzung erfolgt eine Glättung der Seitenwände mittels isotroper Plasmaätzung sowie thermischer Oxidationen. Die Trenches werden konform mit SACVD-Oxid (Sub-Atmospheric Chemical Vapour Deposition) und Poly-Silizium gefüllt, wobei eine möglichst lunkerfreie Auffüllung der Gräben gefordert ist. Die Abb. 2.11 a,b zeigen einen ca. 3,7 µm tiefen Trench mit 170nm SACVD-Oxid für die Isolation der Feldplatte. In einem nächsten Schritt wird der Trench mit n-dotiertem Poly-Si aufgefüllt und mittels selektivem chemisch-mechanischem Polieren (CMP) bis auf die SiO<sub>2</sub> Oberfläche poliert. Für die Dimensionierung der Feldplatte wird das Poly-Si in einem gegenüber dem SACVD-Oxid selektiven Plasma um ca. 1,4µm zurückgeätzt. Eine anschließende naßchemische Entfernung des freiliegenden SiO<sub>2</sub> entlang der Mesa-Gebiete und Trenchkanten führt zu dem in Abb. 2.11 c dargestellten Ergebnis.

Für die spätere Kontaktierung der Feldplatte werden vereinzelte Bereiche der Kompensationstrenches maskiert, wodurch das Poly-Si an der Oberfläche für Kontaktlöcher zugänglich bleibt.

Die Vorbereitung für die Implementierung der Transistorzelle oberhalb der Feldplatte erfolgt mit einer weiteren vollständigen Auffüllung der offenen Trenchstrukturen mit SACVD Oxid, dargestellt in der Abb. 2.11.d.

### Darstellung der wichtigen Prozessschritte für die Herstellung von Split-Gate Strukturen

Abb. 2.11 a) SEM Darstellung einer geätzten Trenchstruktur mit SACVD-Oxid zur Feldplattenisolation

- b) SEM Darstellung einer Trenchstruktur aufgefüllt mit SACVD-Oxid und Poly-Si nach CMP

- c) SEM Darstellung einer Trenchstruktur nach Poly-Si Rückätzung und Entfernung des freiliegenden SACVD-Oxids

- d) SEM Darstellung einer Trenchstruktur nach SiO<sub>2</sub> Auffüllung des oberen Trenchbereichs

- e) SEM Darstellung einer Trenchstruktur nach Rückätzung des SiO<sub>2</sub> mit verbleibendem Restoxid zur Feldplattenisolation

- f) SEM Darstellung von Split-Gate Zellen nach der Implementierung der Gatestruktur mit Gateoxid und planarisiertem Poly-Si

Die gute Konformität des SACVD Prozesses gewährleistet eine Schichtabscheidung ohne Einschlüsse von Hohlräumen (Lunkerbildung). In der nachfolgenden komplexen Technologiesequenz bestehend aus CMP und Plasmarückätzung wird das SiO<sub>2</sub> gleichmäßig, bis auf eine verbleibende Isolationsschicht zur Feldplatte von ca. 400nm, zurückgeätzt. Die Darstellung der Abb. 2.11.e zeigt die Trenchstruktur mit isolierter Feldplatte, vorbereitet für die Einbringung der Transistorzelle.

Der Aufbau des Transistors beginnt mit einer Voroxidation mit nachfolgender naßchemischer Oxidentfernung zur Beseitigung von Kristallschäden an den freiliegenden Si-Oberflächen. Die anschließende Gateoxidation mit darauffolgender Poly-Si Deposition sowie der Poly-Si Dotierung bilden die Schlüsselprozesse für die Prozessierung der Transistorzellen. Ein weiterer CMP-Schritt mit anschließender kurzer Plasmarückätzung dient der Entfernung des Poly-Si auf der Waferoberfläche. Die vollständige Split-Gate Zelle ist in der Abb. 2.11 f dargestellt. Sie stellt das zentrale Element neuer PowerMOS Kompensationsbauelemente dar, die den wesentlichen Teil der F&E Arbeit erfordert hat. Die weiteren nachfolgenden Schritte die p-Body, Source, Kontakt, Metall und Passivierungsprozessmodule entsprechen dem Prozessablauf moderner PowerMOS Bauelementeherstellung und werden nicht weiter ausgeführt.

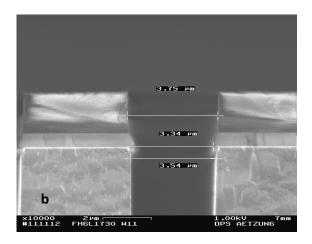

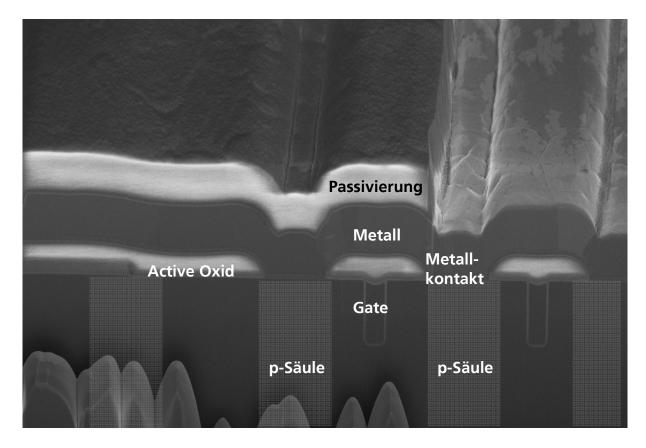

Das fertige Bauelement inklusive der genannten Prozesse für Kontaktierung und Metallisierung des Bauelements ist in den nachfolgenden SEM Schnittbildern der Abb. 2.12 a,b dargestellt. Die Abb. 2.12 a zeigt die vollständige Split Gate Kompensationzelle mit der Kontaktierung der Source-p-Body Mesa-Gebiete. In der Abb.2.12 b ist die Kontaktierung der nach oben geführten Feldplatte gezeigt.

Abb. 2.12 a) Darstellung einer vollständigen Split-Gate Zelle mit Kontaktierung der Source/p-Body Mesa Gebiete

b) Darstellung vollständigen Kompensationszelle mit Kontaktierung der Feldplatte

# 2.4 Elektrische Charakterisierung

Erste elektrische Charakterisierungen wurden nach den wesentlichen statischen Bauelementeparametern durchgeführt.

Der mittlere  $R_{Dson}$  Wert liegt mit 1,14 mOhm, gemessen bei einer Gatespannung von 10V, erwartungsgemäß deutlich niedriger als vergleichbare Werte für Standardbauelemente. Die Schwellspannung befindet sich mit  $V_T = 1,5V$  innerhalb der Spezifikation für diese Spannungsklasse. Die Durchbruchsspannung beträgt ca. 45V und entspricht der Anforderung einer 40V Spannungsklasse. Ausgezeichnete niedrige Werte wurden für die Kanal- und Gate-Leckströme gemessen, die für Kompensationsbauelemente eine besondere Herausforderung darstellen.

Tab. 2.1 Zusammenfassung der statischen Ergebnisse

| Statische<br>Parameter | R <sub>DSon</sub><br>(mOhm) | <b>V</b> <sub>τ</sub> <b>(V)</b> | B <sub>vss</sub> (V) | I <sub>GSS</sub> (nA) | I <sub>DSS</sub> (μA) |

|------------------------|-----------------------------|----------------------------------|----------------------|-----------------------|-----------------------|

|                        | 1,14                        | 1,48                             | 45,7                 | < 10                  | < 10                  |

## 2.5 Zusammenfassung

Im Rahmen der Untersuchungen zu den Split-Gate Kompensationsbauelementen wurden umfangreiche Simulationen durchgeführt und neue Designkonzepte diskutiert und umgesetzt. Hierbei standen insbesondere 3D-Kompensationseffekte für sogenannte Racetrack-Strukturen im Vordergrund. Wie für den Dual-Gate Ansatz wurde auch für die Split-Gate Bauelemente ein Technologieansatz entwickelt und an einem Technologiedemonstrator erprobt. Hierfür wurden spezielle Ätz- und Depositionsprozesse entwickelt und mit einem neuen Integrationskonzept zusammengeführt. Auch hier zeigt sich die Notwendigkeit eines thermo-mechanischen Stressmanagements, insbesondere für tiefe Kompensationsstrukturen.

Aufgrund der hohen technologischen Komplexität sowie den vorangegangenen Erfahrungen mit Dual-Gate Transistoren wurde die Herstellung erster Split-Gate Bauelemente für die Spannungsklasse 40-50V begonnen, skalierbar auf 100V. Hierfür wurde gemeinsam mit dem Industriepartner Vishay ein neuer Technologieansatz erarbeitet und erfolgreich für erste Bauelemente umgesetzt. Auf der Grundlage dieser Ergebnisse werden zukünftig Bauelemente dieser Art in die Produktion überführt und für höhere Spannungen weiterentwickelt.

# 3. Super-Junction Bauelemente

## 3.1 Einleitung

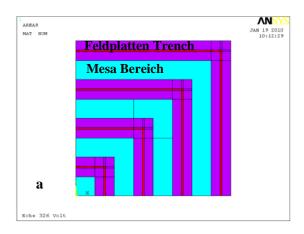

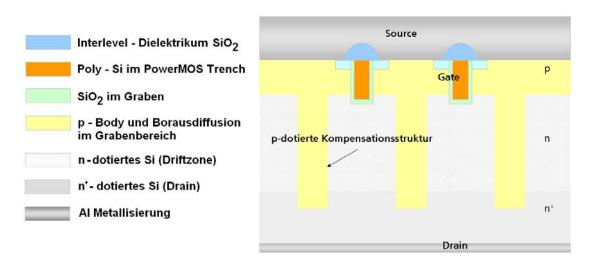

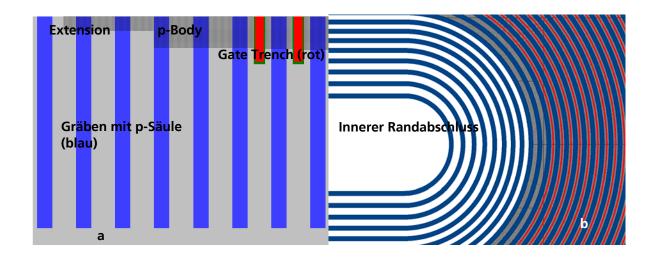

Neben dem Feldplatten-Kompensationsverfahren wurde auch ein epitaktischer Super-Junction Ansatz auf Basis tiefer Trenches untersucht, geeignet für Sperrspannungen oberhalb 200 V. Die Ladungskompensation wird bei diesem Ansatz durch vertikale p – dotierte Strukturen erzeugt. Die Herstellung der p–dotierten Säulen erfolgt durch Auffüllung tiefer Gräben mittels Bor dotierter Siliziumepitaxie (Abb 3.1). Die Transistorstruktur wird, vergleichbar dem Dual Gate Feldplattenansatz, zwischen den Kompensationsstrukturen im Mesabereich platziert. Der Vorteil dieses Verfahrens besteht darin, dass die bei höheren Sperrspannungen zunehmende Trenchtiefe weitgehend frei von mechanischen Spannungen epitaktisch gefüllt werden kann. Gegenüber dem CoolMOS-Verfahren sollte ein technologischer Ansatz geringerer Komplexität für den Spannungsbereich bis ca. 400V untersucht werden mit verbesserter Skalierbarkeit für niedrigere Spannungsklassen.

Abb. 3.1: Prinzipdarstellung eines Super-Junction Transistors mit vertikalen trenchbasierten Kompensationsstrukturen

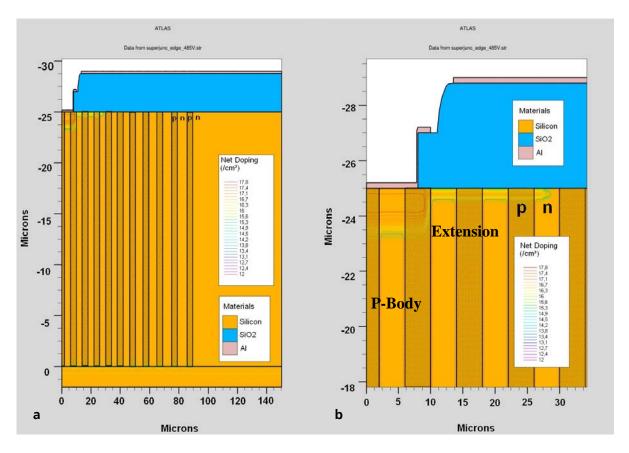

#### 3.2 Simulation

Ausgangspunkt für die Simulationen sind Bauelemente mit einer Durchbruchspannung bis 400 Volt, die eine besondere Randstruktur für die Terminierung des elektrischen Feldes erfordern. Durch die Vorgabe trenchbasierter, epitaktischer Kompensationsstrukturen im Source Bereich des Bauelements war es erforderlich, eine angepasste Randstruktur zu entwickeln, die eine Fortsetzung dieser p-Säulenstruktur berücksichtigt. Durch umfangreiche Simulationen wurde ein Ansatz gefunden, der aus mehreren vertikalen p-Säulen besteht, deren Abstände zum Rand vergrößert werden (Abb. 3.2 a).

Mittels einer weiteren flachen p-Dotierung an der Oberfläche zwischen den Säulenstrukturen ist es möglich mit Hilfe des sogenannten Resurf – Effektes einen effizienten Randabschluss kürzester Randlänge (<100µm) zu realisieren. Dieser p-dotierte Extensionbereich schließt an das p-Body Gebiet an, hat aber eine geringe Dotierung und ist flacher implantiert als der eigentliche p-Body Bereich (Abb. 3.2 b). Der Ansatz des Randabschlusses entspricht dem Junction-Termination-Extension (JTE) Prinzip.

Abb.3.2: a) Gesamtübersicht der Dotierungsverläufe für Simulation des Randabschlusses mit 25µm tiefen p-Säulen

b) Detaildarstellung der Dotierungsverläufe für den p-Body- und Extensionbereich

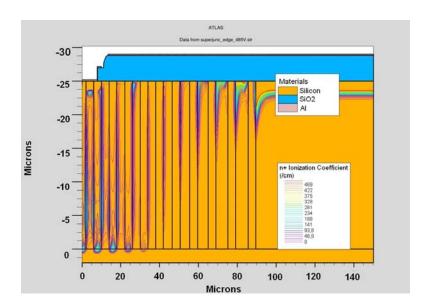

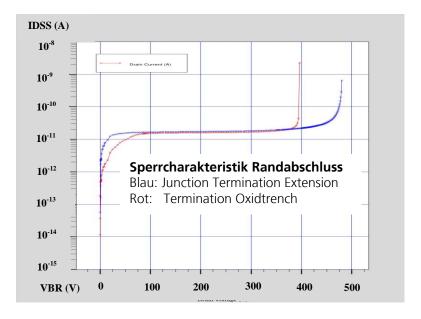

Die Abb. 3.3 zeigt den simulierten Ort des Avalanche-Durchbruchs mittels der Löcherlonisationsrate für eine Säulentiefe von 25µm. Der Durchbruch erfolgt im unteren Bereich der epitaktisch gefüllten p-dotierten Kompensationsgräben bei einer maximalen Durchbruchspannung von 470V, dargestellt in der Sperrcharakteristik gemäß Abb. 3.4. Die Lokalisierung des Durchbruchs im unteren Bereich der p-Säulen ist wünschenswert, da auf diese Weise das Gateoxid des Transistors nahe der Waferoberfläche nicht durch heiße Ladungsträger beeinträchtigt wird.

Abb. 3.3: Simulation p-Säulen Randabschluss mit Junction Termination, Darstellung der Löcher – Ionisationsrate im Durchbruch

Abb. 3.4: Simulation Sperrcharakteristik für P-Säulen Randabschluss mit JTE (blau) und als Referenz breiter SiO<sub>2</sub> Trench (rot)

Für die Wahl der Mesadotierung und der p-dotierten Kompensationsgräben sind folgende Gesichtspunkte wesentlich. Es gilt zunächst die elementare Bedingung der Ladungskompensation :

$$N_A * W_{Graben} = N_D * W_{Mesa} \tag{1}$$

Diese Kompensation kann nur wirken, wenn im Sperrfall die Raumladungszone vollständig von freien Ladungsträgern entleert ist, das heißt, ab einer Sperrspannung von

$$\frac{e * N_A}{\varepsilon} * \frac{w_{Graben}^2}{2} \approx \frac{e * N_D}{\varepsilon} * \frac{w_{Mesa}^2}{2}$$

(2)

Simulationen zeigen, dass die Feldstärkeverteilung am homogensten ist, wenn p– und n– Zonen bei der gleichen Spannung ausgeräumt werden. Daraus folgt, dass bei gleicher Dotierung

$$W_{Graben} = W_{Mesa}$$

(3)

sein sollte. Im Kompensationsfall gilt in der Symmetrieachse einer Zelle für die Feldstärken, wenn x parallel zur Oberfläche ist:

$$E_X = 0 (4)$$

$$\varepsilon_{Si} * \frac{dE}{dy} = Q_{eff} \tag{5}$$

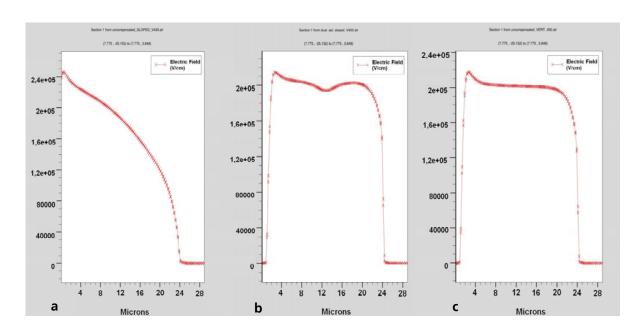

Q<sub>eff</sub> bestimmt sich nach dem Gauß'schen Satz, durch die Bilanz von positiven und negativen Feldlinien, die durch ein Volumenelement am Ort y hindurchgehen. Es ist dann ein annäherndes Rechteckprofil der Feldstärke (wie in einer PIN Diode) erreicht, das bekanntlich die höchste Durchbruchspannung bei vorgegebener Dicke der Raumladungszone zeigt (Abb. 3.5c und Abb. 3.6c, der ideale Fall). Für eine Durchbruchspannung von 470V sind dann 25μm Tiefe der Raumladungszone erforderlich.

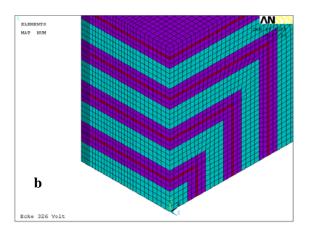

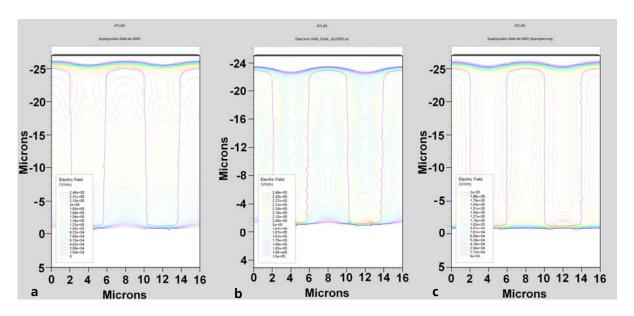

Die Wahl der absoluten Größen von  $w_{Graben}$  und  $w_{Mesa}$  sind durch folgende Überlegung bestimmt: Simulationen zeigen, dass die Feldstärke, die zum lateralen Ausräumen der Raumladungszone erforderlich ist, möglichst klein sein sollte, um Durchbrüche am Rand zu vermeiden. Andererseits ist aber aus technologischen Gründen die Weite des Mesa und somit auch des Kompensationsgrabens auf 4 µm limitiert. Man erhält dann für die gewünschte Spannungsklasse eine optimale Dotierung von 4 x10<sup>15</sup> cm<sup>-3</sup>. In den Abbildungen 3.5a – c und 3.6a – c wird eine weitere Möglichkeit zur Optimierung der Struktur gezeigt: Die Technologie der epitaktischen Grabenfüllung verlangt eine Aufweitung der Kompensationsgräben. Damit ist die Bedingung (1) verletzt. Dem kann durch eine zweistufige Driftzonenepitaxie entgegen gewirkt werden. Bei dieser Epitaxie ist die höhere Dotierung an der Oberfläche, da  $w_{Graben} > w_{Mesa}$ . Abbildung 3.6b zeigt mittels des Kriteriums (5), dass dadurch eine verbesserte Kompensation erreicht wird.

Ohne eine zweistufige Driftzonenepitaxie würden sich die Feldstärke bei aufgeweiteten Gräben einem Dreieckprofil annähern (Abb. 3.5a und Abb. 3.6a). Die Folgen wären unzureichend kompensierte Bauelemente mit einer Durchbruchspannung, die wesentlich kleiner als 470 V ist.

Abb. 3.5: Darstellung des 2D- E-Feldstärkeverlaufs für

- a) aufgeweitete Gräben mit einstufiger n-Driftzonen Epitaxie (25µm)

- b) aufgeweitete Gräben mit zweistufiger n-Driftzonen Epitaxie (25µm)

- c) senkrechte Gräben mit einstufiger n-Driftzonen Epitaxie (25µm)

Abb. 3.6: Darstellung des vertikalen elektrischen Feldstärkeverlaufs in der Mitte der Mesa für

- a) aufgeweitete Gräben mit einstufiger n-Driftzonen Epitaxie (25µm)

- b) aufgeweitete Gräben mit zweistufiger n-Driftzonen Epitaxie (25µm)

- c) senkrechte Gräben mit einstufiger n-Driftzonen Epitaxie (25µm)

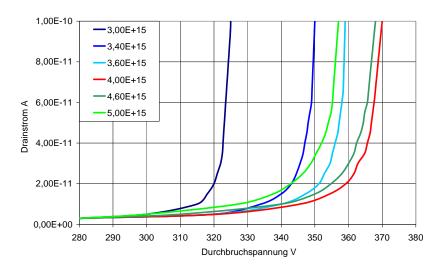

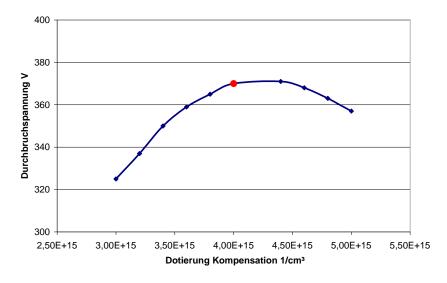

Die Empfindlichkeit der Ladungskompensation gegenüber Dotierungsschwankungen ist in der Abb. 3.8 dargestellt. Zu diesem Zweck wurde die Abhängigkeit der Durchbruchsspannung von der Variationen der p-Säulen Dotierungen für 17µm tiefe Gräben untersucht.

Die Kompensationskurve zeigt ein breites Optimum im Bereich  $4 - 4,5 \times 10^{15}$  cm<sup>-3</sup> mit nur schwacher Änderung der Durchbruchsspannung. Eine Überkompensation bis 10% der optimalen Dotierung von  $4 \times 10^{15}$  cm<sup>-3</sup> hat demnach keinen erheblichen Einfluss auf den Avalanche-Effekt. Es ist deutlich zu erkennen, dass die Überkompensation weniger kritisch ist, als die Unterkompensation im Bereich abnehmender Dotierungskonzentrationen.

Die Reduzierung der Trenchtiefe auf 17µm gegenüber der 25µm tiefen Driftzone wurde aus technologischen Gründen gewählt, um eine zuvor beobachtete Wechselwirkung zwischen dem hoch n-dotierten Substrat mit den p-Dotierungssäulen zu verhindern. Daher werden in diesen Simulationen im Kompensationsfall nur 370V erreicht. Die Abb. 3.7 zeigt die Sperrcharakteristika für unterschiedlich Dotierungskonzentrationen der p-Dotierungssäulen.

Abb. 3.7: Sperrspannungs-Charakteristika für verschiedene p-Säulen Dotierungen

Abb. 3.8: Kompensationskurve in Abhängigkeit der p-Säulen Dotierung, (rot: optimaler Kompensationspunkt)

Die Simulation des spezifischen Einschaltwiderstands  $R_{DSon}$  ergab einen Wert von ca. 7  $m\Omega cm^2$  für eine Sperrspannung von 370V bei einem Zellpitch von 8 $\mu$ m. Dieser Wert liegt um den Faktor 3 unterhalb des sogenannten "silicon limit", dem Driftzonen Widerstand einer idealen, nicht kompensierten Transistorstruktur.

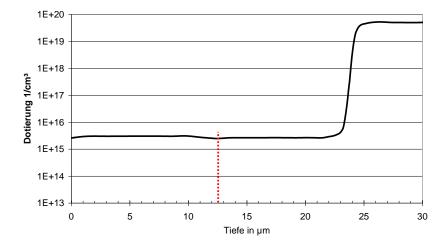

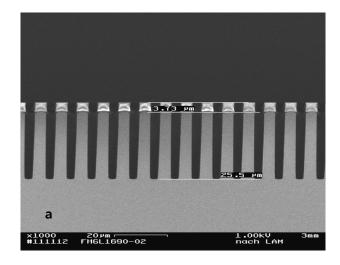

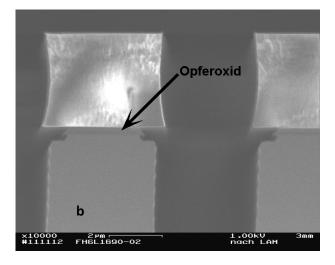

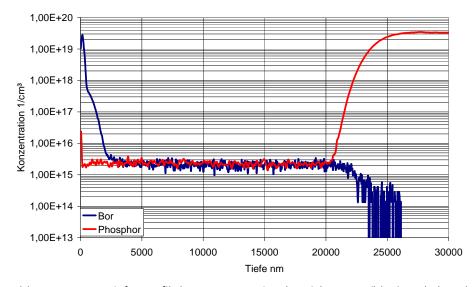

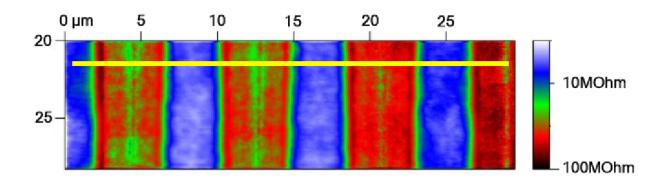

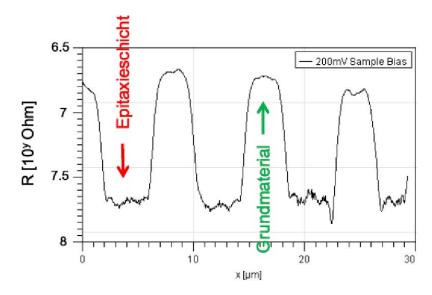

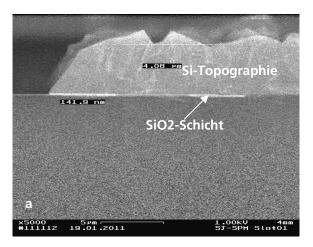

Für die beschriebenen Simulationen wurden ideale Mesa– und p-Säulen Gebiete mit homogener Dotierung gerechnet. Interdiffusion zwischen Mesa- und p-Säulen Bereiche infolge der Epitaxie wurde nicht berücksichtigt, da für die Ladungskompensation die jeweilige Dotierungsdosis entscheidend ist. Die Breite der Mesastrukturen wurde aus technologischen Gründen für die Implementierung der Transistorzelle auf 4,0 µm festgelegt, woraus bei vergleichbaren Dotierungsbedingungen auch eine Grabenbreite von 4µm für die Bor-Epitaxie folgt.