# **Abschlussbericht**

# Teilvorhaben Infineon:

"Erfassung lokaler Werkstoffeigenschaften und Entwicklung neuer Präparationsverfahren"

im industriegeführten Verbundprojekt

Fehlersuche und Fehleranalyse in komplexen Systemen

der Mikro- und Nanoelektronik

(Kurzwort: FULL CONTROL)

Autoren: Klaus Pressel, Walter Mack, Stefan Martens, Bernd Krüger

Geschäftszeichen: 16SV2311 Laufzeit: 1.7.2006 – 31.12.2009

Gefördert vom

Bundesministerium für Bildung und Forschung (BMBF)

Projekträger: VDI/VDE Berlin

# Inhalt

| I.  | Pro                                                                                                                                                                   | ojektbesc             | hreibung                                                                                                                                                                               | S.                   | 3            |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------|

|     | 2.<br>3.<br>4.                                                                                                                                                        | Planung u<br>Wissensc | stellung<br>tzungen, unter denen das Vorhaben durchgeführt wurde<br>und Ablauf des Vorhabens<br>haftlicher und technischer Stand zu Beginn des Projekts<br>narbeit mit anderen Stellen | S.<br>S.<br>S.<br>S. | 5<br>6<br>10 |

| II. | Pro                                                                                                                                                                   | ojektergek            | onisse                                                                                                                                                                                 | S.                   | 15           |

|     | 1.                                                                                                                                                                    | Darstellur            | ng der erzielten Projektergebnisse                                                                                                                                                     | S.                   | 15           |

|     | <ol> <li>Statusanalyse und Definition der Technologieanforderungen in<br/>hoch-integrierten Mikro-/Nanosystemen (einschl. System-in-<br/>Package-Lösungen)</li> </ol> |                       | integrierten Mikro-/Nanosystemen (einschl. System-in-                                                                                                                                  | S.                   | 15           |

|     |                                                                                                                                                                       | 1.2 Testp             | roben                                                                                                                                                                                  | S.                   | 16           |

|     |                                                                                                                                                                       | 1.3.1                 | örungsfreie Fehlerlokalisation und – identifizierung<br>Time Domain Reflektometry<br>Lock-in Thermographie<br>Magnetfeldmikroskopie                                                    | S. 2<br>S. 2<br>S. 2 | 19<br>24     |

|     |                                                                                                                                                                       | 1.4 Neue<br>1.4.1     | Methoden der Zielpräparation<br>Entwicklung neuer Laserstrahl basierter<br>Präparationsverfahren                                                                                       | S. 3<br>S. 3         |              |

|     |                                                                                                                                                                       | 1.4.2                 | ·                                                                                                                                                                                      | S. 3                 | 35           |

|     |                                                                                                                                                                       | 1.4.3                 |                                                                                                                                                                                        | S. 3                 | 38           |

|     |                                                                                                                                                                       | 1.4.4                 | Analyse der "Heat Affected Zone (HAZ)" bei Zielpräparation                                                                                                                             | S. 4                 | 41           |

|     |                                                                                                                                                                       | Zuver                 | ative Analytik für die Untersuchung von<br>lässigkeitsuntersuchungen: Speckleinterferometrie und<br>rmungsmessungen                                                                    | S. 4                 | 45           |

|     |                                                                                                                                                                       | 1.6 Erfass            | sung lokaler Werkstoffeigenschaften                                                                                                                                                    | S. 4                 | 49           |

|     | 2.                                                                                                                                                                    | Zusamme               | enfassende Bewertung der Ergebnisse                                                                                                                                                    | S. :                 | 50           |

| Ш   | . Ve                                                                                                                                                                  | röffentlic            | hungen                                                                                                                                                                                 | S.                   | 52           |

| ΑI  | okü                                                                                                                                                                   | rzungsve              | rzeichnis                                                                                                                                                                              | S.                   | 54           |

# I. Projektbeschreibung

# 1. Aufgabenstellung

### **Motivation:**

Die zunehmende Miniaturisierung mikro-/nanoelektronischer Komponenten bei gleichzeitig immer mehr Integration neuer Funktionalitäten, getrieben von innovativen Produkten der mobilen Kommunikation, erfordert für die Hersteller komplexer miniaturisierter Systeme (insbesondere System-in-Package) immer höheren Aufwand für Fehlerlokalisierung, Zielpräparation, und Fehleranalyse. Diese große Herausforderung ist auch in den internationalen Roadmaps, wie z.B. ITRS, JISSO, iNEMI herausgestellt.

Das vorliegende Teilprojekt von Infineon, das im Rahmen des deutsch/französischen Projekt FULL CONTROL bearbeitet wurde, lieferte für Infineon einen Beitrag zu drei wesentlichen Herausforderungen der Mikro/-Nanosystemtechnik, die auch in internationalen Roadmaps, die die Mikro-/Nanosystemtechnik berücksichtigen, beschrieben sind:

- i) Verbesserung der Zuverlässigkeit, Qualität und Ausbeute, sowie Produktion

- ii) Verbesserung der Methoden der Fehlerlokalisierung inkl. Zielpräparation und Fehleranalyse (das Zusammenwirkung zunehmender Materialvielfalt, auch getrieben durch die Einführung "grüner" Produkte, wird heute in der Industrie zu einer extremen Herausforderung bezüglich Zuverlässigkeit und somit Fehlervermeidung)

- iii) Ermittlung von Materialparametern (z.B. als Eingabewerte für Simulationen)

#### Aufgaben:

In diesem Projekt wurden neue Methoden/Geräte der Fehleridentifikation, Zielpräparation und Fehleranalyse für komplexe mikro-/nanoelektronische Systeme, insbesondere für System-in-Package Anwendungen, entwickelt, angepasst und eingeführt. Infineon arbeitete sowohl an der Entwicklung neuer Methoden als auch an der Untersuchung ihres Potentials für Fehlerlokalisation, Zielpräparation oder Fehleranalyse. Die Methoden wurden hinsichtlich ihrer Bedeutung zur Verbesserung der Zuverlässigkeit von Mikro-/Nanosysteme erforscht und bewertet.

Besondere Ziele des Teilprojekts von Infineon im Rahmen des PIDEA/Euripides Gesamtprojekts FULL CONTROL waren:

- i) Entwicklung/Mitentwicklung, Anpassung und Einführung innovativer Diagnostik und Testmethoden sowie der zugehörigen Geräte im Bereich komplexer Systeme

- zur Lokalisierung und Identifizierung von Fehlern in komplexen Mikro-/Nanosystemen einschließlich elektrischer Fehlerisolation

- zur Zielpräparation von Fehlerstellen in hochintegrierten Gehäusen und Verbindungen (z.B. laser- und ionenbasierende Zielpräparationsmethoden, einschließlich FIB)

- zur Fehleranalyse von komplexen Gehäusen im Mikro-/Nanometer-Bereich, insbesondere an kritischen Verbindungs-/Schnittstellen.

- zur Bestimmung ausgewählter Materialparameter (z.B. auch als Eingabeparameter für Simulationen)

Unterstützung der Entwicklung von gerätetechnischen und von softwaretechnischen Lösungen für die erforderlichen Präparations-, Diagnostik- und Testverfahren, um markttaugliche innovative Produkte im Bereich der analyseorientierten Prüftechnik zu erarbeiten. Eine enge Zusammenarbeit besonders mit den deutschen Gerätehersteller wie Thermosensorik (Innovationen im Bereich thermographischer Fehlerlokalisierungssysteme), Dantec Dynamics (optischer Verformungs-(ionenmesstechnik), und Zeiss NTS und laserstrahlbasierten Zielpräparationstechnik und hochauflösender Analytik, neue komplexe fokussierte Ionenstrahltechnik mit integrierter Analytik, Weiterentwicklung von TEM-Techniken durch Zeiss/IWMH)

- ii) Einsatz der neu entwickelten mikrostrukturellen Diagnostikverfahren zur Untersuchung zuverlässigkeitsbestimmender Prozesse bei der Bauelemententwicklung ("Physics of Failure")

- iii) Bewertung des Einsatzbereichs und Potential der Methoden im Vergleich zu existierenden Methoden.

- iv) Erarbeitung von Lösungen für die Qualitätssicherung und Fehleranalyse, die den zukünftigen Anforderungen an Durchsatz, Effizienz und Zuverlässigkeit in der Fertigung hoch integrierter Mikrosysteme Rechnung tragen.

- v) Erfassung von Werkstoffkennwerten, die als Eingabeparameter für die Simulation geeignet sind, direkt am Bauelement in Korrelation zur Mikrostruktur.

- vi) Integration der Verfahren und Entwicklung gerätetechnischer Lösungen bei Herstellern von Mikrosystemen ("System-in-Package") mit den folgenden Zielstellungen:

- sichere Beherrschung des Werkstoffverhaltens von Packagingkomponenten für die Entwicklung robuster Herstellungsprozesse ("Design for Reliability").

- Kostensenkung bei der Produktentwicklung von hoch integrierten Gehäuse- bzw. Systemlösungen wie Multi-Chip Carriers, Flip-Chips und 3D-Stacks.

- Erweiterung der Integrationsmöglichkeiten bei hochbelasteten Mikrosystemen im Automobilbereich.

- vii) Entwicklung einer methodischen Kette zur Qualitätsabsicherung beim Packaging von Mikrosystemen, die im ersten Schritt die zuverlässige Fehlerlokalisierung, nachfolgend eine effektive und artefaktfreie Zielpräparation, sowie eine hochauflösende Analyse bis in den Nanometerbereich erlaubt (DFA, Design for Failure Analysis).

# 2. Voraussetzungen, unter denen das Vorhaben durchgeführt wurde,

An dem Projekt nahmen jeweils 6 deutsche und 6 französische Partner teil. Davon sind drei Partner aus weltweit anerkannten Forschungseinrichtungen (FhG IWMH, CEA-LETI, CNES Toulouse).

Das Gesamtprojekt bestand aus 4 unterschiedlichen Gruppen von Projektpartnern:

- i) Forschungsinstitute,

- ii) Methoden-Geräteentwickler (Zeiss, Dantec Dynamics, Thermosensorik, Insidix; Infineon hat an der Weiterentwicklung von Methoden entscheidend mitgearbeitet)

- iii) Zulieferern (Orsay Physics, Epsilon) und

- iv) Anbieter/Anwender (Infineon, ELMOS, Atmel/e2v).

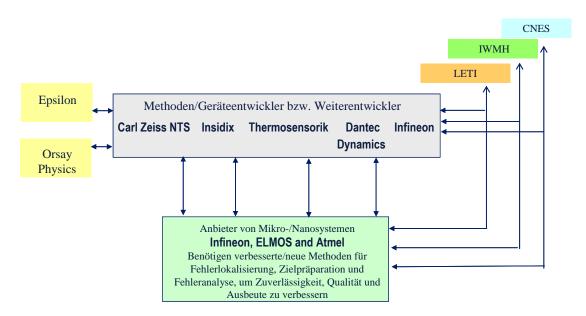

Eine Übersicht der Wechselwirkungen dieser vier Gruppen im FULL CONTROL Projekt zeigt Abbildung 1. In enger Zusammenarbeit sollten zum einen neue Methoden der Fehleranalyse entwickelt werden, zum anderen sollten die Hersteller der Mikro-/Nanosysteme in die Lage versetzt werden, ihre Zuverlässigkeit zu verbessern. Fokus von Infineon im FULL CONTROL Projekt war an Entwicklungen der Methoden entscheidend mitzuarbeiten, sowie die Methoden hinsichtlich ihres Potentials für Fehlerlokalisation, Fehlererkennung, und Zuverlässigkeitsuntersuchungen zu erforschen.

Abbildung 1: Übersicht zur Zusammenarbeit zwischen den Partnern. Die Doppelpfeile zeigen, dass die Partner sich exzellent gegenseitig ergänzen. Die Forschungsinstitute LETI, CNES und IWMH unterstützen sowohl Methoden/Geräteentwicklung als auch die Anbieter von Mikro-/Nanosystemen (SiP).

#### **Projektmanagement:**

Das Projekt wurde durch ein Steuerkommittee unter der Leitung von Zeiss NTS gelenkt. Die 7 Arbeitspakete des Projekts wurden jeweils von einem der Partner geleitet.

# 3. Planung und Ablauf des Vorhabens,

Das Gesamtprojekt FULL CONTROL war in sieben Arbeitspakete AP1 bis AP7 gegliedert, die wiederum in mehrere Teilaufgaben unterteilt sind. Infineon arbeitete an allen 7 Arbeitspaketen mit, um zum einen die Weiter-/Neuentwicklung der verschiedenen Methoden voranzutreiben, zum anderen mit verbesserter Fehleranalyse Zuverlässigkeit, Qualität und Ausbeute zu verbessern.

# Übersicht Arbeitspakete und Zeitplan

Die folgende Tabelle 1 gibt eine Übersicht über die Arbeitspakete des Projekts gemäß der deutschen Zusammenfassung. Infineon ist an allen Arbeitspaketen beteiligt und leitet speziell das für den Gesamtablauf des FULL CONTROL Projekts sehr wichtige Arbeitspaket 1.

Tabelle 1: Übersicht über die Arbeitspakete des Projekts

(x) Der Leiter des Arbeitspakets ist in der rechten Spalte unterstrichen (D = Deutschl., F = Frankreich)

| Arbeits- | Titel / kurze Beschreibung                                                 | involvierte Partner             |

|----------|----------------------------------------------------------------------------|---------------------------------|

| paket #  |                                                                            |                                 |

| AP1      | Statusanalyse und Definition der Technologie-                              | <u>Infineon (D)</u>             |

|          | anforderungen in hochintegrierten Mikro-/Nanosystemen                      |                                 |

|          | (einschl. System in Package-Lösungen)                                      | alle Partner sind eingebunden   |

|          | Aufgabe 1.1 Statusanalyse existierender Methoden,                          |                                 |

|          | Vergleich mit Wettbewerb, Definition von                                   |                                 |

|          | Anforderungen für Zuverlässigkeit                                          |                                 |

|          | Aufgabe 1.2 Regelmässige Statusanalyse und                                 |                                 |

|          | Beobachtung des Wettbewerbs                                                |                                 |

|          | Aufgabe 1.3 Regelmässige Definition, Aktualisierung                        |                                 |

|          | und Herstellung von Teststrukturen                                         |                                 |

|          | Zerstörungsfreie Fehlerlokalisierung und -identifizierung                  | CNES(F)                         |

| AP2      |                                                                            |                                 |

|          | Aufgabe 2.1 Fehlerlokalisierung mittels "Time Domain Reflektometrie (TDR)" | Carl Zeiss NTS (D)<br>ELMOS (D) |

|          | Aufgabe 2.2 Fehlerlokalisierung mittels Lock-in-                           | Infineon(D),                    |

|          | Thermographie                                                              | Thermosensorik(D),              |

|          | Aufgabe 2.3 Fehlerlokalisierung mittels Magnet-                            | IWMH(D),                        |

|          | mikroskopie                                                                | Atmel (F),                      |

|          | Aufgabe 2.4 Fehlerlokalisierung mit akustischen                            | Insidix(F),                     |

|          | Verfahren in Kombination von Experiment                                    | LETI (F),                       |

|          | und Modellierung                                                           | Epsilon(F)                      |

|          | Aufgabe 2.5 Fehlerlokalisierung mittels automatisierter                    | . ,                             |

|          | lichtmikroskopischer Verfahren und                                         |                                 |

|          | Bildanalyse für die Sicherung der                                          |                                 |

|          | Zuverlässigkeit in der Wafer level                                         |                                 |

|          | Package (WLP-) Fertigung                                                   |                                 |

| AP3 | Neue Methoden der Zielpräparation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Carl Zeiss NTS (D)                                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|     | Aufgabe 3.1 Entwicklung neuer laserstrahlbasierter Präparationsverfahren  Aufgabe 3.2 Optimierung und Automatisierung von großflächigen Ionenstrahlpoliturverfahren für REM- Querschliffe  Aufgabe 3.3 Entwicklung eines Hochstrom-systems der fokussierenden Ionenstrahltechnik (FIB) für Packagingapplikationen  Aufgabe 3.4 Optimierung und Anpassung der FIB- Präparationsmethodik für hoch auflösende Untersuchungen an Grenz- flächen der Aufbau- und Verbindungs technik (REM, TEM)                                                                       | Infineon (D), ELMOS (D) IWMH (D) Atmel (F), CNES (F), Orsay Physics (F)                                                        |

| AP4 | Innovative Analytik für die Untersuchung von Zuverlässigkeitsproblemen der Aufbau- und Verbindungstechnik in hochintegrierten Mikro- und Nanosystemen  Aufgabe 4.1 Komplexe 3D FIB-Analyse für hoch integrierte Mikro-/Nanosysteme Aufgabe 4.2 Neue integrierte Methoden für die automatisierte Identifizierung von intermetallischen Verbindungen in AVT- Grenzflächen Aufgabe 4.3 Thermische Laserstimulation Aufgabe 4.4 Optimierte Fehleranalyse mittels Speckle- Interferometrie, Topographie- und Ver- formungsmessungen (TDM) und 3D- Grauwertkorrelation | IWMH (D),  Carl Zeiss NTS (D),  ELMOS (D)  Infineon (D),  Dantec Dynamics (D)  Insidix (F),  Epsilon (F)  CNES (F),  LETI (F), |

| AP5 | Erfassung lokaler Werkstoffeigenschaften  Aufgabe 5.1 Untersuchung der mechanischen Eigenschaften von Drahtbondkontaktie rungen  Aufgabe 5.2 Einsatz von optischen Feldmessverfahren für die lokale Bestimmung von Wärme ausdehnungskoeffizienten und der Grenzflächenfestigkeit  Aufgabe 5.3 Messung lokaler Aufladungen in MEMS-Bauelementen                                                                                                                                                                                                                   | LETI (F)  IWMH (D) ELMOS (D) Infineon (D) Dantec Dynamics (D) Thermosensorik (D) Insidix (F) Epsilon (F)                       |

| AP6/AP7 | Anwendung von Fehleranalyseverfahren für die Sicherung der Zuverlässigkeit von hochintegrierten                                                                                                                        | Atmel (F)                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|         | komplexen Mikro-und Nanosystemen (AP6 Pidea+)                                                                                                                                                                          | Infineon (D)<br>IWMH (D),        |

|         | Aufgabe 6.1 Identifizierung neuer Ausfall- und Fehler mechanismen relevant in zukünftigen hochintegrierten Mikro-/Nanosystemen                                                                                         | Insidix (F),<br>LETI (F)         |

|         | Aufgabe 6.2 Einsatz und Untersuchung optimierter<br>Fehleranalyseverfahren für hochintegrierte<br>Mikro-/Nanosysteme                                                                                                   | ELMOS (D)                        |

|         | Erarbeitung eines abgestimmten und verallgemeinerten<br>Konzeptes für die Fehlerlokalisierung und<br>-analyse in hochintegrierten Mikro-/Nanosystemen<br>(AP7 Pidea+)                                                  | alle Partner sind<br>eingebunden |

|         | Aufgabe 7.1 Bewertung der Ergebnisse der AP 2-6 und Ableitung von Schlussfolgerungen für neue marktfähige Fehleranalysetechniken                                                                                       |                                  |

|         | Aufgabe 7.2 Definition eines verallgmeinerten abgestimmten Konzeptes für die Fehler analyse und diagnostische Techniken für zukünftige hochintegrierte Mikro-/ Nanosysteme einschließlich System in Packaging-Lösungen |                                  |

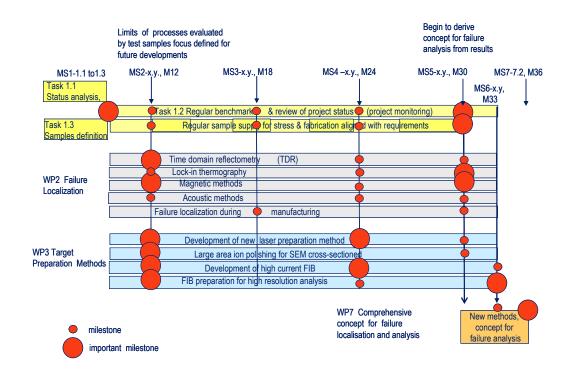

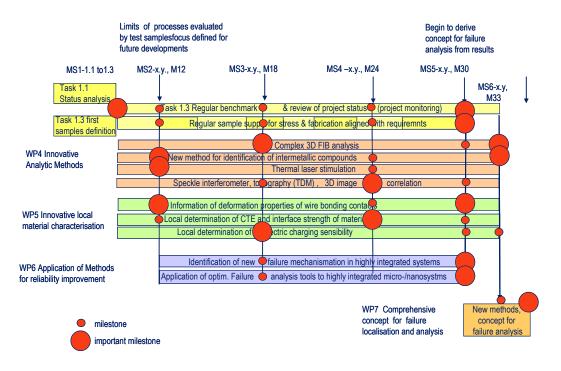

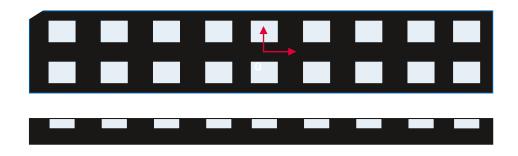

### Abbildung 2 zeigt den Gesamtarbeitsplan (Meilensteinplan)

Abbildung 2: Zeitplan gemäß PIDEA+ Antrag (Hinweis: WP = AP): die Meilensteine MS sind wie folgt definiert: MS1 = nach 3 Monate, MS2 = nach 12 Monate, MS3 = nach 18 Monate, MS4 = nach 24 Monate, MS5 = nach 30 Monate, MS6 = nach 33 Monate und MS7 = nach 36 Monate. Meilenstein MS2 -1.3 bezeichnet z.B. Meilenstein 2 zur Aufgabe 3 im Arbeitspaket AP 1 (x = Nummer eines AP und geht von 1-7, y ist Nummer der Teilaufgaben und kann Werte von 1-4 annehmen).

# 4. Wissenschaftlicher und technischer Stand zu Beginn des Projekts

Ein unumkehrbarer Trend bei mikro-/nanoelektronischen und mikro-/nanomechanischen Systemen ist die zunehmende Miniaturisierung, verbunden mit Integrationsdichte bei gleichzeitigem Funktionalitätsgewinn. zielgenaue Entwicklung auf Kundenwunsch hin erfordert eine hohe Flexibilität und führt zu einer stark ansteigende Variantenvielfalt. Diese Entwicklung erstreckt sich über alle Bereiche, von der Verbraucher ("Consumer")- bis hin zur Automobilgrundlegende Zuverlässigkeit, Ausbeute Elektronik. Qualität und sind Voraussetzungen für die Entwicklung komplexer innovativer Micro-/Nanosystem-Anwendungen und werden zunehmend zu einer extremen Herausforderung.

Eine Besonderheit der Aufbau- und Verbindungstechnik von "System-in-Package (SiP)" bzw. Mikro-/Nanosystemen ist die Vielfalt an notwendigen Materialien, vom metallische Verbindungsstellen bis hin zu Polymeren verschiedensten aufeinander folgenden Schichten. Dies führt zu Herausforderungen für die Fehleranalyse. Die Notwendigkeit für neue bzw. verbesserte und angepasste Methoden zur Fehleridentifikation und Fehleranalyse für künftige Gehäuse, vor allem für SiP Anwendungen wurde in einem "White Paper" veröffentlicht durch das Internationale SEMATECH "Assemby Analytic Forum Analytical Tool Roadmap White Paper im Juni 2004 - als dringend herausgestellt (siehe http://www.sematech.org/docubase/document/4532atr.pdf). Diese Initiative wurde durch die ITRS ("International Technology Roadmap of Semiconductors"; http://www.itrs.net) ausgelöst, wo schon in der Ausgabe von 2003 die Notwendigkeit verbesserter Fehleranalysemethoden herausgestellt wurde. Auch die neue Ausgabe der ITRS, veröffentlicht im Dezember 2009, unterstreicht weiterhin die Notwendigkeit verbesserter Fehleranalysemethoden, besonders für mikro-/nanoelektronische Systemanwendungen, insbesondere wo System-in-Package Aufbauten benötigt werden. Das Ganze ist getrieben von zunehmender Funktionalität insbesondere durch die Mobilkommunikation.

Es sei an dieser Stelle nochmal darauf hingewiesen, dass der Begriff "System-in-Package" Mikro-/Nanosysteme umfasst, d.h. die Kombination von Silizium mit MEMS Komponenten oder anderen Sensoren, Bio- und optoelektronischen Komponenten usw. Insbesondere am Standort Regensburg fokussiert sich Infineon auf Sensoren und Module, d.h. u.a. Mikro-/Nanosystemlösungen (SiP Lösungen) wie am Beispiel in Abbildung 3 dargestellt.

Abbildung 3: Beispiel Reifendrucksensor mit mehreren Komponenten in einem Gehäuse.

Im Gegensatz zur "Front-end" (meist Si-basierende IC Herstellung) Technologie von Mikro-/Nanosystemtechnik, wo leistungsfähige hochauflösende Nano-Analyseverfahren die zugehörigen Fehlerlokalisierungsund Präparationstechniken (wie z.B. "Focused Ion Beam" (FIB) und Transmissions-Elektronenmikroskopie (TEM)) bis hin zum Betrieb in der Linie verfügbar und qualifiziert sind, ist dies für die Gehäusetechnologien nicht der Fall. In den Silizium "Front-end" Technologien gibt es eine Vielzahl von Methoden und Erfahrungen, die aber nicht ohne weiteres auf die schnelle und anspruchsvolle Entwicklung von komplexen "System-in-Package" bzw. Mikro-/Nanosystemaufbauten übertragen werden können. So sind zum Beispiel Material-Abtragraten, wie sie in der Silizium-IC Produktionstechnik vorkommen, nicht vergleichbar mit den notwendigen Abtragraten im Packaging-Bereich, die zudem hohe Inhomogenitäten (z.B. schon im "Mold Compound" allein) in Folge stark unterschiedlicher Materialien aufweisen.

Bedingt durch die hochintegrierten Komponenten kommt die zeitraubende und kostenintensive Hintereinanderschaltung verschiedenster Analysemethoden zum Einsatz. Es war unbedingt erforderlich, zum einen bestehende Verfahren an die Bedingungen der "Aufbau- und Verbindungstechnik (Packages)" anzupassen sowie neue, auf das Package zugeschnittene Analyseverfahren zu entwickeln bzw. weiterzuentwickeln. Durch die heute zur Verfügung stehenden Laserstrahl- und lonenstrahlverfahren oder Techniken wie die Kopplung von fokussierter lonenstrahltechnik (FIB) und "Electron Back Scattering Deflection (EBSD)" ergaben sich neue innovative Möglichkeiten.

Prüfverfahren, die es gestatten, in geeigneten Bereichen bauteilabhängige Werkstoffparameter zu erfassen, waren nur in Ansätzen vorhanden. Stattdessen waren Messungen im Allgemeinen an deutlich größeren technologisch nicht relevanten Ersatzkomponenten durchgeführt. Die bestimmten werkstoffmechanischen Kennwerte waren auf das Bauteil im Allgemeinen nicht oder nur sehr eingeschränkt übertragbar.

Es mussten zuverlässig lokale Struktur- und Materialparameter als Eingabewerte für entwicklungsbegleitende Simulationen ermittelt werden, um so zum "Design for Reliability" schon beim Systementwurf beizutragen. Hersteller von Mikrosystemen und hoch integrierten elektronischen Baugruppen können so entscheidend Entwicklungskosten sparen und die Zuverlässigkeit unter Einsatzbedingungen erhöhen.

Es sei hier besonders herausgestellt, dass zunehmende Anforderungen von Kunden bezüglich Zuverlässigkeit und Qualität, besonders aus der Automobilindustrie, extreme Anstrengungen und Anforderungen an Infineon stellen. Eine geeignete Fehleranalyse ist hier von herausragender Bedeutung.

Die zukünftigen Systemlösungen führen zwangsweise zu neuen Fragestellungen und Herausforderungen im Hinblick auf Zuverlässigkeit und Fehleranalyse z.B.:

- Welcher der vielen unterschiedlichen Systemkomponenten (z.B. IC Chip, Sensor, MEMS) hat die Fehlfunktion?

- Liegt der Fehler am Chip oder an den Verbindungen (z.B. Drahtverbindungen, "Bump", Substrat)?

- => Frage nach der (elektrischen) Lokalisierung

- Wie lege ich den lokalisierten Fehler zur weiteren Analyse frei?

=> Frage nach der artefaktfreien/rückwirkungsfreien Präparation an der neuen Materialvielfalt, die das hochintegrierte Mikro-/Nanosystem mit sich bringt.

- Wie simuliere ich ein hochintegriertes Mikrosystem verlässlich?

=> Frage nach der Bestimmung lokaler Materialeigenschaften und somit Berücksichtigung der Fertigungseinflüsse.

# Besondere Defizite in der Analysetechnik waren:

- artefaktfreie Präparation von komplexen Materialsystemen bei hochintegrierten Mikrosystemen (Defekte freilegen zur weitergehenden Analyse oder Bestimmung lokaler Materialparameter innerhalb des Packages),

- Lokalisierungsmethoden für elektrische Fehler (Kurzschlüsse, Leckströme, Unterbrechungen) für hochintegrierte Mikrosystem v.a. für deren interne Verbindungen zwischen den Subkomponenten (Chips, MEMS, Passive etc...),

- Methoden zur Messung lokaler interner Materialparameter nach Durchlauf der Fertigungsprozesse als realistische Eingabewerte für zuverlässige Simulationen,

- Methoden zur Analyse der Mikrostruktur metallischer Verbindungen zum besseren Verständnis von Ausfallmechanismen an komplexen Mikrosystemen,

- Methoden zur Quantifizierung und Lokalisierung von Gehäuse-internen thermomechanischen Spannungen zur Verbesserung von Gehäusedesign und Materialauswahl.

## Verwendete Fachliteratur sowie wichtigste Informations- und Dokumentationsdienste:

Wichtiges Informationsmaterial im Assembly und Packaging sind die weltweit stattfindenden internationalen Konferenzen.

Für FULL CONTROL wurden insbesondere folgende Konferenzen besonders berücksichtigt:

- i) ECTC (Electronics Component Technology Conference)

- ii) ISTFA (International Symposium for Testing and Failure Analysis)

- iii) EUROSIME (Thermal, Mechanical and Multiphysics Simulation and Experiments in Micro/Nanoelectronics and Systems)

- iv) ESREF (European Symposium Reliability of Electron Devices, Failure Physics, Analysis)

## Internationale Roadmaps und damit verbundene Kontakte:

- i) ITRS (siehe <u>www.itrs.net</u>, Infineon ist u.a. in der Assembly & Packaging Arbeitsgruppe vertreten und engagiert sich insbesondere bei den Themen Systemintegration)

- ii) JISSO (internationales Konsortium, das insbesondere in Japan vorangetrieben wird; JISSO ist ein japanisches Kunstwort für "Total System Solution")

- iii) iNEMI (International Electronic Manufacturing Initiative; siehe www.inemi.org)

Verfolgung von Arbeiten an internationalen Instituten von Universitäten und Forschungseinrichtungen außerhalb Europa, z.B. PRC (Package Research Center, Georgia Tech, U.S.A.), IME (Singapore), ITRI (Taiwan), KAIST (South Korea).

#### 5. Zusammenarbeit mit anderen Stellen.

Für die Aufgaben des Projekts waren eine Vielzahl von Herausforderungen zu lösen und vielseitige Erfahrungen nötig, die in Deutschland nicht alleine vorhanden waren. Es wurden teilweise neue Analysemethoden oder Zulieferkomponenten evaluiert, für die es in Deutschland nicht die nötige Kompetenz gab. Für die Bearbeitung wurde daher eine europäische Kooperation im Rahmen des Eureka Pidea/Euripides-Programms initiiert. Besonders herauszustellen sind folgende Zusammenarbeiten, die eine Vielzahl von Synergien ergaben:

- i) Das CEA-LETI ist ein in Europa führendes Forschungsinstitut im Bereich Mikroelektronik/Mikrosystemtechnik. Seine besondere Stärke ist, dass es sowohl "Front-end" als auch "Back-end" Technologie besitzt und Entwicklungen im Bereich der Analytik vorantreibt. Daraus resultierend besteht hier, neben Erfahrungen in der Si-Technologie, insbesondere auch ein weit reichender Kenntnisstand für MEMS und Mikrosystemtechnik. Am LETI existierende Analysemethoden wurden in das Projekt einbezogen und hinsichtlich Anwendungen für 3D Integration evaluiert.

- ii) Die Zusammenarbeit mit dem CNES in Toulouse war von besonderem Interesse, da dort schon sehr viel Erfahrung im Bereich Fehleranalyse und Zuverlässigkeit für die besonders hohe Anforderungen stellenenden Luft- und Raumfahrtanwendungen vorhanden sind und deshalb eine sehr hoch entwickelte Fehleranalyse zur Verfügung steht. In Kooperation mit dem CNES wurde der Einsatz der "Scanning Magnetic Microscopy" mit SQUID für die Fehlerlokalisierung in komplexen Packaginglösungen untersucht. Dieses Verfahren stellt eine alternative Möglichkeit dar, die die Entwicklungen mit den Projektpartnern Thermosensorik und Dantec Dynamics ergänzten. Im Rahmen der Zusammenarbeit sollte das Know-how der beiden französischen Spitzenforschungsinstitute CEA-LETI und CNES und der FhG für optimale Synergien verwendet werden um dadurch wichtige Schritte hinsichtlich Marktvorteile für zuverlässige "System-in-Package"- und Mikrosystemprodukte zu erreichen.

- iii) Für die Entwicklung geeigneter Präparationstechnologien von der Gehäuseöffnung und Gehäusevorpräparation bis hin zur Zielpräparation im Sub-Mikrometerbereich ist eine stufenweise, aufeinander abzustimmende Prozessfolge erforderlich. Das "Know how" und die Weiterentwicklungen des CNES in Toulouse im Bereich der Lasertechnologien ("Laserablation") stellten einen wichtigen Schritt in dieser Kette dar, an dem die Ionenstrahltechniken der Fa. Zeiss anschließen sollten und die gerätetechnische Integrationsfähigkeit des Gesamtprozesses zu prüfen war.

- iv) Zur Unterstützung der gerätetechnischen Entwicklungen von Zeiss war für die neue Ionenstrahlätztechnik eine spezielle Hochstromquelle unverzichtbar. Die französische Firma Orsay Physics entwickelte in diesem Projekt die nötige Hochstromquelle als Zulieferer für Zeiss. Diese Kooperation stärkte insbesondere die Position von Zeiss als FIB-Hersteller am Weltmarkt.

- v) Die Firma Insidix ist eine noch junge Firma, die sich mit zerstörungsfreien Methoden, wie der Röntgen- und akustischen Mikroskopie, zur Untersuchung von Grenzflächen beschäftigt. Insidix hat eine neue Methode entwickelt, die die Messung der Deformationen von elektronischen Bauelementen in x, y, z-Richtung vor und nach dem Assembly, sowie bei unterschiedlichen Temperaturen und

Temperaturgradienten (TDM) ermöglicht. Dadurch können die Temperatur-Ausdehnungskoeffizienten (CTE) lokal gemessen werden. Die Fähigkeiten dieser Methode wurde bezüglich eines Einsatzes für SiP und Mikrosysteme erforscht. In Kombination mit "Scanning Acoustic Microscopy" gab es Möglichkeiten, elastische/plastische Verhalten an Grenzflächen zu ermitteln. Die TDM Methode sollte Hinblick auf Identifizierung von Fehlern und lokaler Materialcharakterisierung in hochintegrierten Gehäusen weiterentwickelt werden. Es war die Chance, dass diese Verfahren komplementär und ergänzend zu den Methoden der Firma Dantec Dynamics eingesetzt werden könnten.

- vi) Die Firma Epsilon hat spezielle Algorithmen und Software Module für Infrarot Kartographie entwickelt. Eine Kopplung mit thermischen Verfahren eröffnete neue Möglichkeiten. Epsilon arbeitete eng mit Insidix zusammen und die Softwareentwicklungen konnten neue Wege zur Fehleranalyse eröffnen (z.B. bezüglich Finite Elemente Simulationen an Grenzflächen zur Erklärung von Delaminationen). Die Nutzung der Lösungen für die Fa. Thermosensorik wurde evaluiert.

- vii) Die Entwicklungen der deutschen Geräte- und Messtechnikhersteller (Zeiss, Dantec Dynamics, Thermosensorik) sollten französischen Firmen wie z.B. Atmel/e2v nahe gebracht werden (Förderung des schnellen Aufbaus eines Marktes).

# II. Projektergebnisse

# 1. Darstellung der erzielten Projektergebnisse

Das Projekt war in 7 Arbeitspakete (siehe Kapitel I) unterteilt. Infineon arbeitete an allen 7 Arbeitspaketen mit. Infineon fokussierte sich besonders auf die Arbeitspakete 2-4, steuerte zum Teil das Projekt als Leiter von AP1 und lieferte Beiträge u.a. mit Testchips und Bewertungen (zu AP5), aber auch zu den restlichen Arbeitspaketen AP6 und AP7. Im folgenden werden die von Infineon im FULL CONTROL Projekt erzielten Ergebnisse zusammengefasst. Die Projektergebnisse des gesamten Konsortium wurden in zwei öffentlichen Workshops am Fraunhofer IWM Halle (18.9.2008) Organisator: Matthias Petzold) und bei Infineon/München (19.11.2009, Organisator: Klaus Pressel) vorgestellt. Infineon veröffentlichte hier insgesamt 7 Beiträge (siehe Veröffentlichungen [1-3, 8-11]).

# 1.1 Statusanalyse und Definition der Technologieanforderungen in hoch-integrierten Mikro-/Nanosystemen (einschl. System-in-Package Lösungen) (AP1.1, AP1.2)

An diesem Projektteil arbeiteten unter Koordination von Infineon alle Partner mit. Folgende Punkte wurden festgelegt:

- Definition von wichtigen und neuen Fehlertypen aus Sicht von Mikro-/Nanosystem-Herstellern (war Basis einer zielgerichteten Entwicklung der Methoden im Projekt) Beispiele von möglichen Fehlern: Bruchstellen ("cracks"), Delaminationen an Grenzflächen z.B. zwischen gestapelten Si-Chips, Chips und MEMS-Komponenten, offene Leiterbahnen oder solche mit erhöhten Widerständen, Kurzschlüsse, etc.

- 2. Definition künftiger Anforderungen mit 5-10 Jahren Ausblick, Bewertung von Marktvorhersagen und Technologie "Roadmaps"

- 3. Identifizierung bestehender Lücken ("gap analysis") und Grenzen existierender Methoden.

- 4. Festlegung erforderlicher Leistungsparameter für die zu entwickelnden Geräte und Entwicklungsschritte

Regelmäßige Statusanalyse und Beobachtung des Wettbewerbs:

An dieser Aufgabe arbeiteten alle Projektpartner mit und sorgten für eine regelmäßige Aktualisierung der Projektarbeit. Hier wurden vor allem die Arbeitspakete aufeinander abgestimmt werden, was u.a. auch wesentlich für einen optimalen Wissenstransfer war. Alle Partner lieferten hier unter Leitung von Infineon Zuarbeiten. Regelmäßige Überprüfung der in Teilaufgabe 1.1 festgelegten Parameter und Aufgaben.

# 1.2 Testproben (AP1.3, AP2)

Die Arbeiten beinhalteten insbesondere:

- Regelmäßige Definition, Aktualisierung und Herstellung von Teststrukturen

- Entwicklungen und Herstellung von Probeaufbauten wurden während der Projektlaufzeit kontrolliert und an die Methodenentwicklung angepasst.

- Infineon stellte hier solche Testaufbauten her, die für Untersuchungen mit mehreren Verfahren geeignet waren, aber nichts direkt mit einem Produkt zu tun haben. Spezielle Testaufbauten, z.B. mit gezielt eingebauten Kurzschlüssen für TDR (Time Domain Reflektometrie), die nur für einzelne Methoden relevant waren, wurden in den methodenspezifischen Arbeitspaketen aufgeführt.

- Bereitstellung nötiger Teststrukturen mit definierten Materialparametern und Fehlern zur Quantifizierung der Leistungsfähigkeit oder auch Kalibrierung (Materialparameter mussten teils vorher von Infineon ausgemessen werden).

- Beispiele für Teststrukturen: verschiedene zwei oder dreifach gestapelte Komponenten in einem Gehäuse (siehe a) oder b) unten), die ein Mikro-/Nanosystem bilden (Auswahl erfolgte unter Berücksichtigung typischer Fehlerquellen für bestehende und künftige Anwendungen.

Die Definition der Testproben führte im Wesentlichen zu zwei Vorgehensweisen:

- Zur Weiterentwicklung der Präparationsverfahren (Laserablation und lonenstrahlverfahren bei CNES Toulouse, ZEISS Oberkochen) wurden zunächst reine Materialproben (ohne elektrische Funktion) hergestellt, um Anlagenparameter zu optimieren und grundsätzlichere Erfahrung zur Eignung der Verfahren zu sammeln. Bei den Proben handelte es sich um Testkörper aus typischen Materialien der Gehäusetechnologie:

- Moldingcompounds (Pressmassen)

- Chipkleber, Klebertapes

- Verkapselungsmaterialien wie Silikongele

- Optisch transparente Harze

- Chipträger wie Metall-Leadframes, Glasfaserverbund-Substrate

- Interconnect-Materialien wie Gold-/Aluminiumdrähte

- Lotlegierungen (bleifrei)

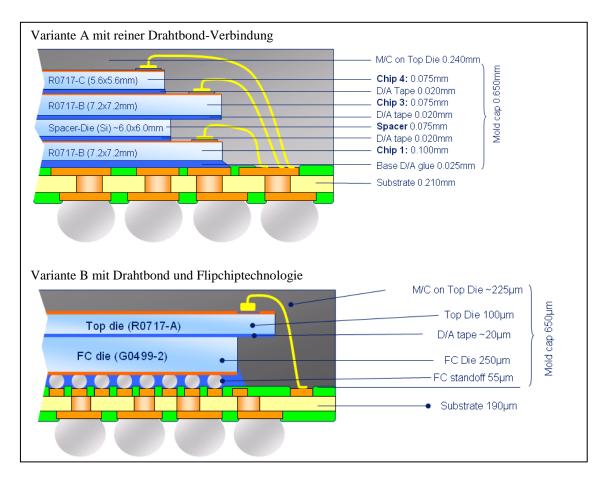

- Zur Untersuchung der Präparationsverfahren wurden sog. "Device-Dummies" aufgebaut - d.h. Bauteile ohne elektrische Funktion jedoch mit neuester Gehäusetechnologie. Sie dienten dazu. die Eignung Präparationsverfahren im komplexen Materialmix von Mikrosystemen zu untersuchen (z.B. bei "Stacked Dice" Technologie das Ablationsverhalten der im Materialverbund Pressmasse/Silizium/Klebertape/ Laser Silizium/Kleber/Substrat). Hierfür wurden folgende Testvehikel von Infineon aufgebaut: Gehäusetyp P-TFBGA-417.

Abbildung 4: Beispiel eines System-in-Package (SiP) Testvehikel.

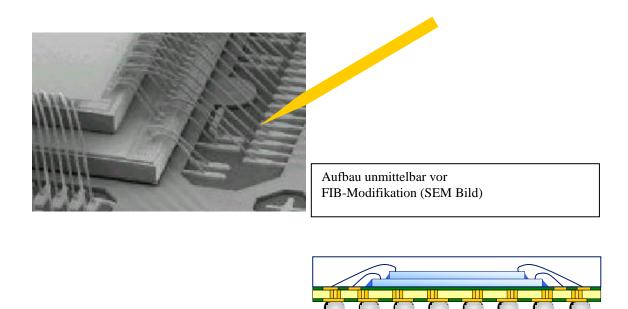

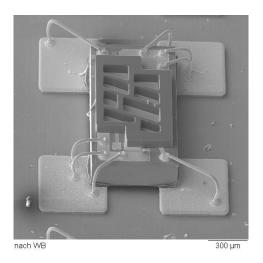

Weiterentwicklung zerstörungsfreien Lokalisierungsmethoden der elektrischer Fehler wurde vereinbart, Bauteile mit elektrischer Funktion herzustellen, eingebaute elektrische Fehler die gezielt enthielten (Leckstrompfade, Leiterbahnunterbrechungen etc.). Das hierzu verwendete Mikrosystem enthielt zwei gestapelte Chips mit speziellen Teststrukturen. Der "Einbau" der elektrischen Fehler erfolgte sowohl direkt beim Drahtbonden der Chips als auch danach durch Modifikation der Interconnects mittels FIB (Focused Ion Beam) im Fehleranalyselabor von Infineon in München. Anschließend wurden die modifizierten Bauteile umspritzt (Molding) und fertig prozessiert. Die Bauteile wurden sodann an die involvierten Projektpartner (Workpackage 2) zum Test Ihrer Lokalisierungsmethoden verteilt.

Abbildung 5: Beispiel eines Aufbaus von System-in-Package Testproben vor FIB der Modifikation; rechts im Bild der schematische Querschnitt des Aufbaus.

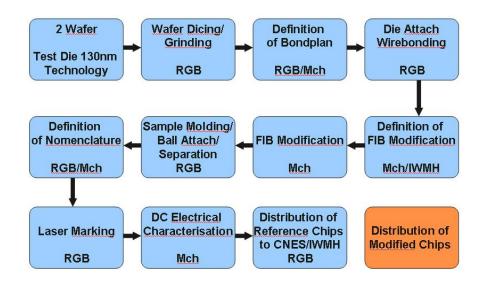

Nachfolgend sind die einzelnen Prozessund Abstimmungsschritte wiedergegeben. Die einzelnen Phasen, insbesondere die Fehlererzeugung, stellte auch für die Fehleranalytik Abteilungen von Infineon Regensburg (RGB) und Infineon München (Mch) eine Herausforderung und einen Lernprozess dar. Auf die gewonnenen Erkenntnisse und Erfahrungen konnte aber im weiteren Verlauf des Full Control-Projekts und danach zurückgegriffen werden.

Abbildung 6: Prozeßfluß für Aufbau der SiP Testproben; neben Infineon in Regensburg (RBG) und Infineon München (Mch) unterstützte auch das FhG IZM (IWMH) den Probenaufbau.

Im Rahmen von FULL CONTROL wurden weiterhin von Infineon eine Vielzahl spezieller Probenpräparationen für verschiedene Versuchsdurchführungen durchgeführt (z.B. bei Zeiss, Dantec, Insidix, FhG IWMH, Thermosensorik). Dazu wurden Proben der unterschiedlichen, in komplexen SiP vorkommenden, Package-Materialien (Mould Compound, Leadframes, Bonddraht, Lotmaterial) präpariert. Außerdem wurden komplette SiP Aufbauten (Variante A, Abbildung 4) für die Laserversuche bei Zeiss aufgebaut und bereitgestellt.

# 1.3 Zerstörungsfreie Fehlerlokalisation und – identifizierung (AP2)

# 1.3.1 Time Domain Reflectometry (AP2.1)

Ein wichtiger Fokus von Infineon war die Erarbeitung und Anwendung des Verfahrens der TDR ("Time Domain Reflectometry") für System-in-Package Anwendungen. IFX hat präparierte Teile geliefert und Ergebnisse interpretiert und bewertet. Ein wesentlicher Beitrag war die Optimierung der experimentellen Aufbauten und die instrumentellen Änderungen zur Erweiterung der Anwendungsbereiche sowie erste Tests zu Simulationen für ein besseres Verständnis der Grundlagen.

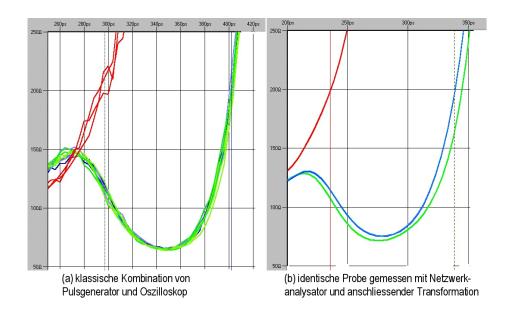

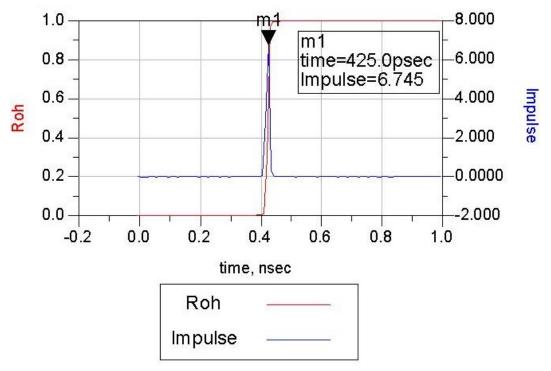

Abbildung 7: Vergleich zweier Methoden zur Messung von TDR-Echosignalen

In einer umfangreichen Vergleichsstudie wurden zwei verschiedene Ansätze zur Messung von TDR-Echosignalen ausgewertet: a) das klassische Verfolgen des reflektierten Spannungsverlaufs eines Spannungspulses in Echtzeit mittels eines Hochfrequenz-Oszilloskops, b) das Ausmessen von S-Parametern – also den Reflektionsfaktoren einzelner ebener Wellen konstanter Amplitude und Frequenz – mittels eines Netzwerkanalysators. An Beispielen wurde gezeigt, dass die Bestimmung im Zeit- und im Frequenz-Raum völlig äquivalent und ohne

Qualitätsverlust mittels Fourier-Transformation ineinander umwandelbar ist. Die klassische Methode ist dabei limitiert durch Jitter des Pulsgenerators und der Triggerung auf diesen Puls, der auch bei der aktuellen Gerätegeneration die zeitliche Auflösung auf ca. 10 psec begrenzt. Die seguentielle über längere Zeit integrierende Bestimmung der S-Parameter stößt bis in Sub-Picosekunden-Bereiche vor (siehe Beispielaufnahmen oben). Auch bei der Bandbreite bis 67 GHz, der Dynamik von bis zu 100 dB und der genaueren Kalibrierungsmöglichkeit, ist der Netzwerkanalysator überlegen. Lediglich die Anschaulichkeit und der einfachere Messablauf sprechen für die Echtzeit-Variante. Um das Potential dieser Methode auszureizen, wurde ein Messaufbau mit optisch kontrollierten Mikromanipulatoren und Hochfrequenz optimierten Nadeln in GSG(Ground-Signal-Ground)-Anordnung zusammengestellt.

Erste Tests verschiedener Simulationsansätze wurden begonnen. Zum einen ausgehend von schematischen Schaltungen, aber auch mittels komplexer 3D-FEM-Modelle. Die beste Vorgehensweise wurde erarbeitet und mit Vergleichen zum Experiment ermittelt. Das Verständnis der dahinterstehenden Physik dieses Ansatzes war ein weiteres Ziel.

Zunächst war der Fokus bei Time Domain Reflectometry (TDR) vor allem auf instrumentelle Optimierung und Vervollständigung der Aufbauten gelegt. In der nachfolgenden zweiten Projektphase wurden danach verschiedene Methoden eingesetzt, um Signale nachträglich ohne Informationsverlust zu bearbeiten und durch Simulation zu erklären.

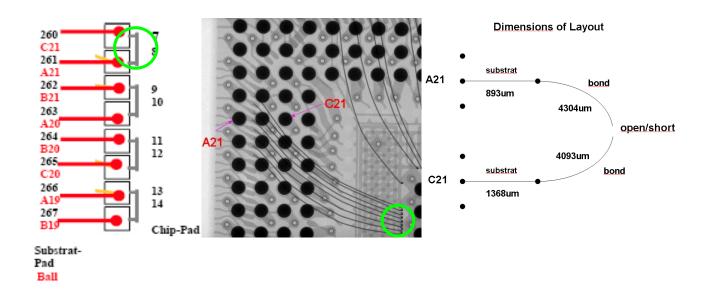

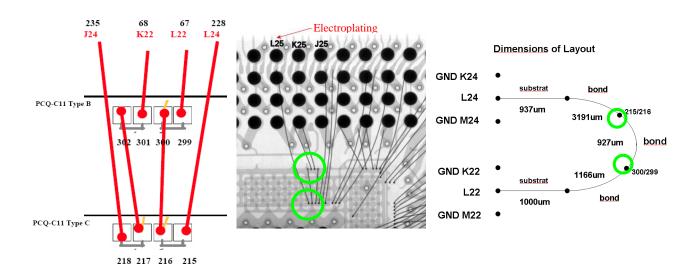

Die dabei gewonnenen Kenntnisse konnten erfolgreich bei der nachfolgend beschriebenen Anwendung von TDR an System-in-Package-(SiP)-Testproben genutzt werden (zu Aufbau und Herstellung der SiP-Testproben mit definierten elektrischen Fehlern siehe 2. Zwischenbericht). Abbildung 8 zeigt den prinzipiellen Aufbau, das Röntgenbild und die relevanten Pfadlängen für das TDR-Signal.

Abbildung 8: Prinzipieller Aufbau, Röntgenaufnahmen und relevante Pfadlänge einer SiP-Testprobe mit eingebauten elektrischen Fehlern (Leiterbahnunterbrechung, Leiterbahnkurzschluss zwischen Drahtbondpads)

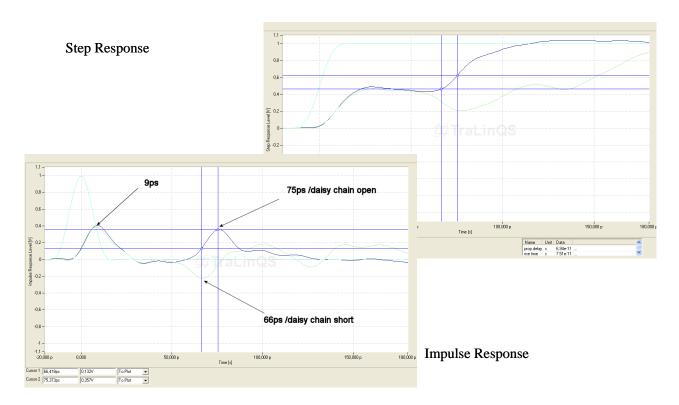

Die Messergebnisse zeigen deutliche Unterschiede in der elektrischen Pfadlänge zwischen Testproben mit Leiterbahnunterbrechungen und Leiterbahnkurzschlüssen zwischen Drahtbondpads (Abb. 9).

Abbildung 9: TDR-Messergebnisse zeigen deutliche Unterschiede zwischen Leiterbahnunterbrechungen und Leiterbahnkurzschlüssen zwischen Drahtbondpads

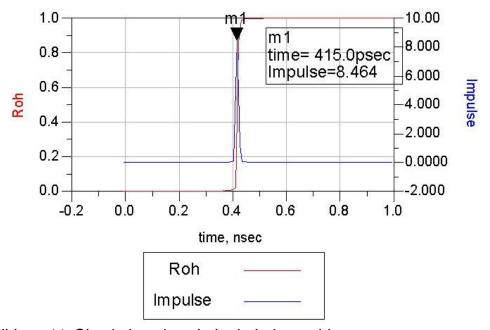

Die gemessenen Impulsgeschwindigkeiten für das Substratmaterial liegen bei ca. 200 µm/ps und 151 µm/ps für die Drahtbondverbindungen. Gemessene Pfadlängenunterschiede zwischen Bauteilen mit Leiterbahnunterbrechungen und Leiterbahnkurzschlüssen ließen sich in Simulationen mit dem Einfluss der Streukapazität bei Leiterbahnunterbrechungen erklären (Abbildungen 10-12 unten).

### Simulation Set-up (with C = open at Bridge; without C = short at Bridge)

Abbildung 10: Simulations-Schema

## Simulation: Short at Bridge

Abbildung 11: Simulation eines Leiterbahnkurzschlusses

#### Simulation: Open at Bridge

Abbildung 12: Simulation einer Leiterbahnunterbrechung

Auch die Nachverfolgung von Strompfaden auf verschiedenen Chips wurde in "Stacked Die" SiP-Testproben erfolgreich demonstriert. Der Aufbau ist in Abb. 13 gezeigt.

Abb. 13: Prinzipieller Aufbau, Röntgenaufnahmen und relevante Pfadlänge von Drahtbondverbindungen über die verschiedenen gestapelten Chips der SiP-Testprobe

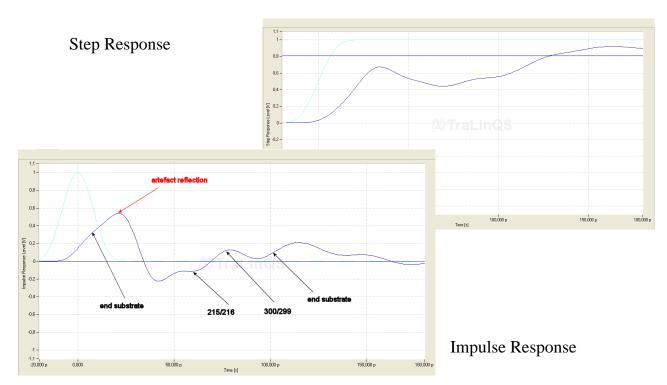

Die Messungen an der SiP-Testprobe zeigten gute Ergebnisse beim Nachverfolgen des Strompfades durch das Substrat und die einzelnen Siliziumchips. Auch konnten Artefakte eliminiert werden, die durch die Galvanisierung verursacht werden. Die Messungen der Impulsgeschwindigkeiten ergaben ca. 200  $\mu$ m/ps im Substrat und 155  $\mu$ m/ps in den Bonddrähten.

Abbildung 14: TDR-Messergebnisse SiP-Testprobe mit gestapelten Siliziumchips

#### 1.3.2 IR-Lock-In Thermographie (AP2.2)

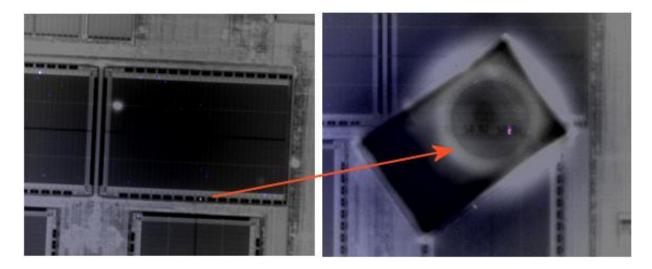

Bei der Infrarot (IR) Lock-in Thermographie wurde durch Einsatz einer von Infineon hergestellten Siliziumlinse (solid immersion lens, SIL) für reduzierte Bildfelder eine Auflösungssteigerung erreicht. Bei Einsatz in Fehleranalysen konnte so die Genauigkeit der Lokalisierung von Wärmequellen bis auf ca. 1 µm gesteigert werden.

Im Rahmen des FULL CONTROL Projekts wurde eine Thermographie-Variante weiterentwickelt, die Wärmestrahlung mit Hilfe von Infrarot-Kameras mittels eines besonders empfindlichen Lock-in Verstärkungsverfahrens detektiert.

Bei Infineon wurde dazu die vom Projektpartner Thermosensorik bereitgestellte Kamera in verschiedenen erweiterten Situationen eingesetzt. Zum einen konnte eine von Infineon hergestellte Siliziumlinse als Solid Immersion Lens (SIL) genutzt werden. Dabei wird für ein reduziertes Bildfeld eine Auflösungssteigerung durch eine Erhöhung der optischen numerischen Apertur erreicht. Im Einsatz bei Fehleranalysen

im Labor konnte so die Genauigkeit der Lokalisierung von Wärmequellen bis auf ca. 1 µm gesteigert werden (siehe Beispiel Abb.15).

Abbildung 15: Beispiel für die Verbesserung der Genauigkeit der Lokalisierung von Wärmequellen.

In Zusammenarbeit mit dem verantwortlichen Projektpartner IWM Halle und dem Projektpartner Thermosensorik GmbH hat Infineon die räumliche Auflösung der Lock-In Thermographie durch den Einsatz sogenannter SIL-Linsen (Solid Immersion Lens) um den Fakter 3,5 steigern können.

Zur weiteren Optimierung wurden dem Fraunhofer IWMH im Anschluss weitere Proben zur Verfügung gestellt. Zur Ermittlung von Phasenverschiebung und Wärmeleitfähigkeitskoeffizienten wurden reine Pressmassen-Proben (Mold Compounds) angefertigt. Durch das Dünnschleifen auf unterschiedliche Dicken konnten so die Phasenverschiebungen in Abhängigkeit der Pressmassendicke gemessen werden und stehen nun als Kalibrierdaten für zukünftige Messungen zur Verfügung.

Das Fraunhofer IWMH untersuchte die Fehlerlokalisation nicht nur durch Pressmassen, sondern auch durch komplette SiP-Aufbauten (System-in-Package). Daher sind Messungen von Phasenverschiebungen und Wärmeleitfähigkeitskoeffizienten durch komplette Package-Aufbauten in sogenannter "stacked Die"-Technologie notwendig. Hierfür wurden dem Fraunhofer IWMH ebenfalls Pressmassenproben mit eingebetteten, in 3D gestapelten Siliziumchips zur Verfügung gestellt (s. Abbildung 16).

Abb. 16: Gemoldete "stacked dies" Aufbauten mit 2 (oben) bzw. 4 gestapelten Siliziumchips zur Vermessung von Phasenverschiebung und Wärmeleitfähigkeit beim Fraunhofer IWMH.

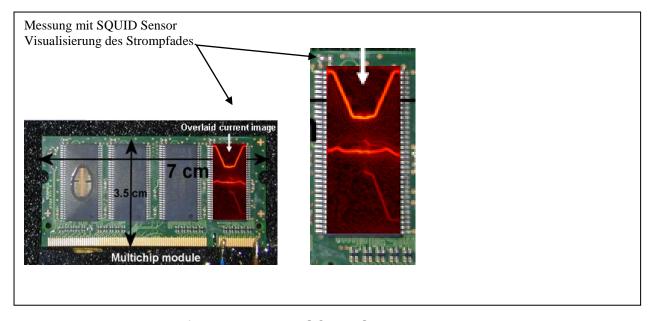

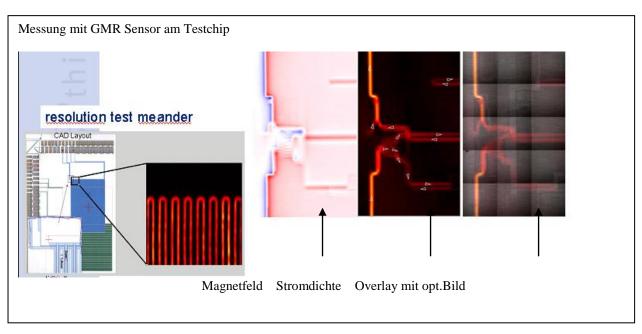

#### 1.3.3 Magnetfeldmessungen (AP2.3)

Bei den SMM Messungen wurden zwei kommerziell verfügbare Magnetfeld Sensoren getestet:

- A) SQUID Sensor (Superconducting Quantum Interference Device)

- B) GMR Sensor (Giant Magneto-Resistive)

Als Testproben dienten u.a. Multichipmodule (Speichermodule) und spezielle Auflösungsproben.

Abbildung 17: Beispiel für Messung mit SQUID Sensor

Abbildung 18: Messung mit GMR Sensor am Testchip

Aus den Messungen bei Infineon wurden folgende Erkenntnisse gewonnen: SQUID-Sensor: Bevorzugter Einsatz bei Mikrosystemen in Gehäusen und Modulen

- Räumliche Auflösung liegt bei 20 µm (Limitiert durch ca. Sensorabstand/4)

- Empfindlichkeit ~ 20 nA bei 100 μm Sensorabstand (Magnetfeld 3,7 nT)

- Bonddrähte o.ä. erfordern einen Abstand von 0,5...1 mm

- Momentane Grenze f

ür Messung von Wechselstr

ömen 20 kHz

- Limits der Scan-Bewegung (momentaner x-y-Tisch):

100 mm x 100 mm; 0,5 μm min. step in x/y; 0,1 μm min. step in z

GMR-Sensor: Bevorzugter Einsatz auf Chip-Ebene

- Räumliche Auflösung < 200 nm

- Empfindlichkeit ~50 μA (momentane Geometrie erlaubt Abstände <10 μm)

- Momentane Grenze f

ür Messung von Wechselstr

ömen 100 kHz (mit Lock-in Technik)

- Limits der Scan-Bewegung (momentaner Piezo-kontrollierter x-y-Tisch):

100 μm x 100 μm; 2 nm min. step

Für die Weiterentwicklung der SMM Methode wurden mehrere Ansatzpunkte gesehen:

- Weitere Miniaturisierung der Sensoren für geringere Arbeitsabstände

- Verbesserung der Feldinversion (Algorithmen) mit angepassten Filterfunktionen (Rauschunterdrückung)

- Quantifizierung bei Nahfeldbedingungen (Arbeitsabstand < = räuml.Auflösung)</li>

- Erfassung der x / y Magnetfeldkomponenten durch Integration weiterer Sensoren mit unterschiedlicher Orientierung.

Deutliche Steigerung des Signal-zu-Rausch-Verhältnis bei der Magnetfeldmessung mittels GMR-Sensoren. Zusammen mit der Entwicklung einer Präparationsmethode zum sicheren Dünnen des Silizium-Substrats ist nun auch die Aufnahme von Magnetfeldbildern und damit Strompfaden durch die Chiprückseite möglich (AP 2)

Zunächst wurden zum Teilbereich Magnetfeldmessung die technologischen Grenzen und aktuellen Auflösungsvermögen erarbeitet, um klare Strategien zur Weiterentwicklung der Methodik zu entwickeln.

In weiteren Arbeiten konnte durch Geometrieoptimierung des GMR-Sensors das Signal-zu-Rausch-Verhältnis abhängig von der Geometrie bis um den Faktor 3 deutlich gesteigert werden. Zusammen mit der Entwicklung einer Präparationsmethode zum sicheren Dünnen des Silizium-Substrats bis auf wenige Mikrometer erlaubte dies die Aufnahme von Magnetfeldbildern und damit Strompfaden auch durch die Chiprückseite. Die ebenfalls verfeinerte Quantifizierung durch Kurvenanpassung ermöglichte nun auch die Bestimmung von Stromstärken und Distanzen innerhalb von komplex verzweigten Strompfaden.

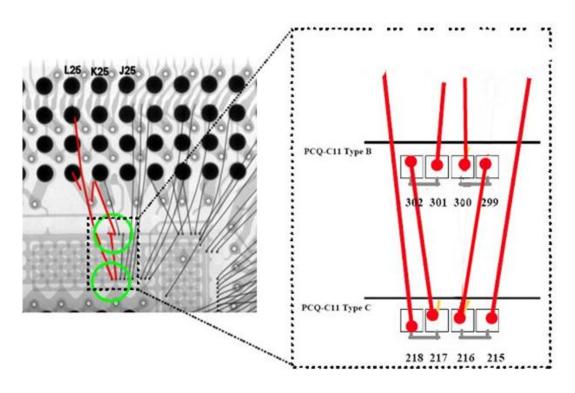

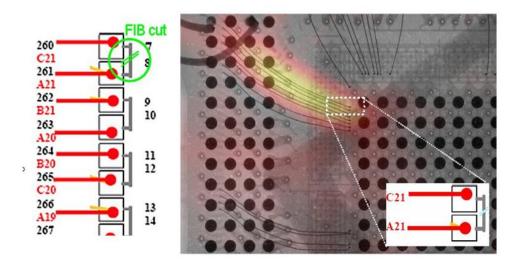

Im Rahmen der bei Infineon geleisteten Arbeit zum Arbeitspakte 2.3 wurden die Stromverteilungen in kompliziert aufgebauten SiP-Bauteilen ("Stacked Package") aufgenommen. Dabei wurden wiederum die SiP-Testproben mit definierten elektrischen Fehlern verwendet.

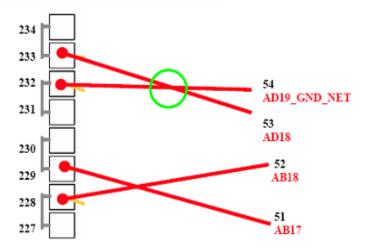

Es wurden beispielsweise Kurzschlüsse zwischen Drahtbondverbindungen simuliert, indem Bonddrähte gekreuzt wurden und der dabei entstehende elektrische Kontakt den Kurzschluss darstellt (Abb. 19). Des Weiteren wurden Leiterbahnunterbrechungen (Open/Unterbrechungen im Strompfad) mittels Magnetfeldmessungen untersucht.

Die kurzgeschlossenen Strompfade (Shorts) wurden mit einer Wechselspannung mit niedriger Frequenz (wenige kHz) betrieben. Während die Leiterbahnunterbrechungen (Opens) mit einem Hochfrequenzfeld im Radiowellenlängenbereich betrieben wurden. Mit dem magnetischen Mikroskop wurde die Verteilung des Magnetfelds bestimmt. Aus dieser wurden dann die Stromverteilungen errechnet und die Strompfade visualisiert.

Abb. 19: Prinzipdarstellung der SiP-Testproben mit gekreuzten Bonddrähten mit elektrischem Kontakt zur Simulation von Kurzschlüssen zwischen Drahtbondverbindungen

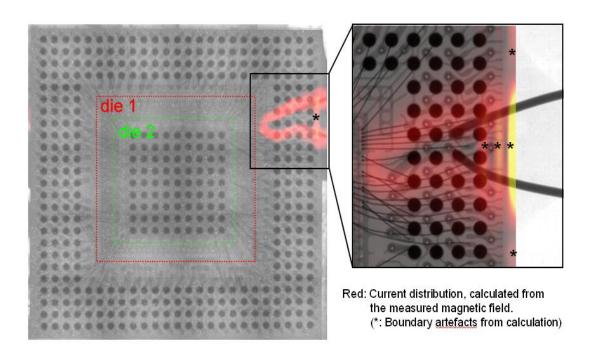

Die sehr beeindruckenden Ergebnisse der gemessenen Stromverteilungen sind in Abb. 20 und Abb. 21 darstellt, inkl. einem Vergleich der Stromverteilung mit dem im Röntgenbild eingezeichneten Strompfad. Aus der gemessenen Stromverteilung kann der Kurzschluss eindeutig den gekreuzten und elektrisch kurzgeschlossenen Drahtbondverbindungen zugeordnet werden.

Abbildung 20: Gemessene Stromdichte, überlappt mit Röntgenbild

Abbildung 21: Vergleich der gemessenen Stromverteilung mit dem Strompfad, der im Röntgenbild (rechts) eingezeichnet ist

In weiteren Versuchen wurde evaluiert, ob Kurzschlüsse zwischen Bondpads zu detektieren sind (siehe Abb. 22). Die gemessene Stromverteilung zeigt, dass beide Siliziumchips des Stacked-Package-Aufbaus in den Strompfad des Kurzschluss-Stromes involviert sind. Durch Vergleich mit dem Package-Aufbau kann die Position des Kurzschlusses dem Bereich der Bondpads zugeordnet werden (siehe Abb. 23).

Abbildung 22: Strompfad des Kurzschluss-Stromes eingezeichnet in das Röntgenbild (links)

Abbildung 23: Errechnete Stromverteilung im SiP-Bauteil

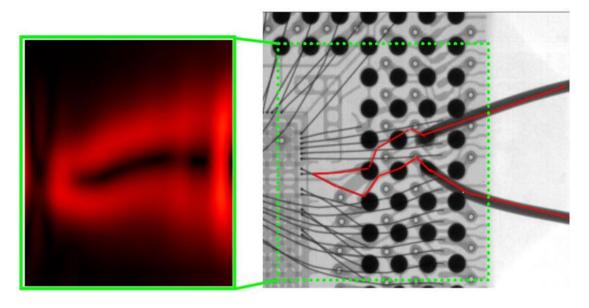

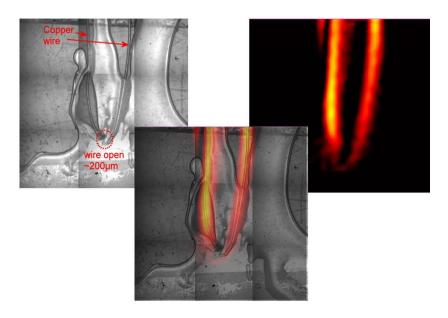

Außerdem wurde versucht, Leiterbahnunterbrechungen (Opens) in SiPs mit einem Hochfrequenzfeld detektieren. Dazu wurden diese im Radiowellenlängenbereich betrieben. Abb. 24 zeigt die Resultate in einer Kupferdraht-Teststruktur nach partiellem Öffnen. Dabei wird die Leiterbahnunterbrechung als lokal erniedrigte Stromdichte erkennbar (Abb. 24).

Abb. 24: Leiterbahnunterbrechung (Open) präpariert in einer Kupferdraht-Teststruktur (links), gemessene Stromdichteverteilung (rechts), sowie die Überlagerung mit dem optischen Bild (mitte).

Die Technik wurde ebenfalls auf Leiterbahnunterbrechungen in SiP-Bauteilen angewendet. Der durch das Hochfrequenzfeld induzierte Strom in die durch einen FIB-Schnitt unterbrochen Leiterbahn ist in Abb. 25 visualisiert. Zusammenfassend lässt sich sagen, dass die Lokalisierung von Leiterbahnunterbrechungen in SiPs mittels Magnetfeldmessungen erfolgreich demonstriert werden konnte.

Abb. 25: Durch einen FIB-Schnitt präparierte Leiterbahnunterbrechung (Open) in einem SiP-Bautei; die Stromdichteverteilung überlappt mit dem entsprechendem Röntgenbild (rechts)

# A1.4 Neue Methoden der Zielpräparation

#### 1.4.1 Entwicklung neuer Laserstrahl basierter Präparationsmethoden

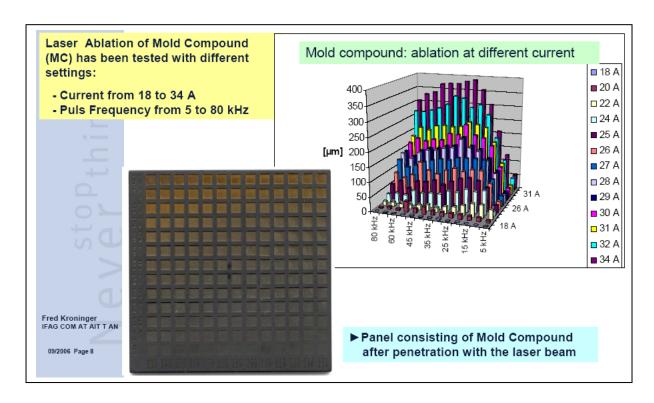

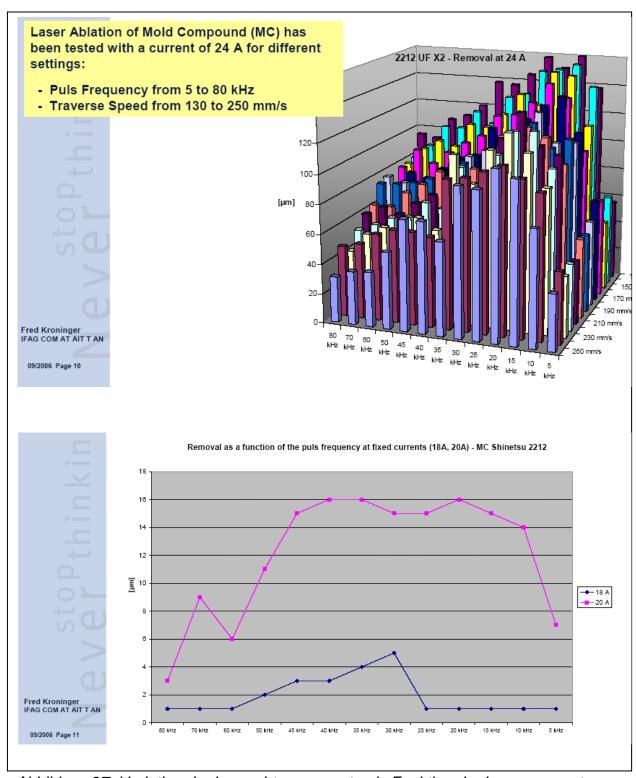

Infineon verfügt über einen Infrarotlaser zur Präparation von Mikrosystemen. Essentiell war hier die systematische Bestimmung der Ablationseigenschaften für die typischen Materialien, die beim Packaging von Mikrosystemen Anwendung finden. Hierzu wurden z.B. Materialproben von Pressmassen in Plattenform verwendet. Typische Parameter der Laserquelle sind Strom, Pulsfrequenz und Scangeschwindigkeit des Strahls.

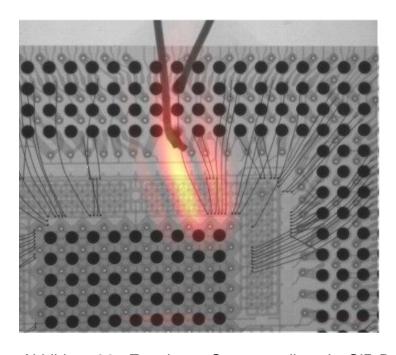

Abbildung 26: Beispiele für Ablation von Moldcompounds mit unterschiedlichen Laserparametern: Strom und Pulsfrequenz. Unten ist ein Panel nach Durchdringung von Laserstrahlung gezeigt.

Abbildung 27: Variation der Laserabtragungsrate als Funktion der Laserparameter

### **Laser-Präparation**

Zur Untersuchung der Präparationsverfahren wurden sog. "Device-Dummies" aufgebaut – d.h. Bauteile ohne elektrische Funktion jedoch mit neuester Gehäusetechnologie. Sie dienen dazu, die Eignung der Präparationsverfahren im

komplexen Materialmix von Mikrosystemen zu untersuchen (z.B. bei "stacked Dies" Technologie das Ablationsverhalten der Laser im Materialverbund Pressmasse/ Silizium/Klebertape/ Silizium/Kleber/Substrat). Hierfür wurden 2 Testvehikel im Gehäusetyp P-TFBGA-417 von Infineon aufgebaut. Beide Varianten wurden auch dem CNES in Toulouse zur Evaluation des Femtosekunden-Lasersystems zur Verfügung gestellt. Diese Aufbauten waren analog Abbildung 4. Als Testaufbauten u.a. zur Evaluation der unterschiedlichen Laserquellen wurden 2 Varianten aufgebaut: Variante A = Stapelung von Chip in 3D mittels Drahtbonden; Variante B: Stapelung von Chips durch gemischte FlipChip/Drahtbond Technologie.

Ausgehend von einer ausführlichen Marktuntersuchung wurde eine Reihe von Laserherstellern und Lasersystemlieferanten für die Untersuchung der unterschiedlichen Laserquellen ausgewählt. Systeme von TRUMPF (1064nm-Mikrobearbeitungslasers) und von ROFIN SINAR Laser GmbH (532nm und 355nm) wurden auf Ihre Anwendbarkeit hin untersucht. Es wurden Untersuchungen zu Picosekundenlasern und Excimerlasern erarbeitet. Von Infineon Regensburg wurde auch die Analyse der mit dem CNES-Femtosekunden-Lasersystem bearbeiteten Proben übernommen und dem CNES zur Verfügung gestellt.

## Laser-basierte Zielpräparation in 3D System-in-Package Aufbauten

Im folgenden werden die wichtigsten Ergebnisse der Öffnung von Moldcompounds (MC) mit verschiedenen Lasern zusammengefasst. Die Entfernung von MC von Gehäusen um die darin eingebetteten Chips freizulegen, ist ein wichtiger Teil Zielpräparation der Fehleranalyse [zu Details siehe Referenzen [6,8].

Im Rahmen des FULL CONTROL Projekts wurden verschiedene Laserquellen untersucht (zu Details siehe auch Refs. [6,8]).

- Femto-Sekunden Laserquelle

- Picosekunde Laserquelle

- Exzimer Laserquelle

- Dioden gepumpter Festkörperlaser

Insbesondere wurden der Einfluss der Pulsdauer und die Wellenlänge auf die Abtragung auf verschiedene Komponenten in gestapelten System-in-Package Aufbauten untersucht.

Zusammen fassend ergaben sich folgende Ergebnisse:

Ultrakurze Laserpulse im Femto-Sekunden Bereich sind nicht für Abtragung des Moldcompounds (MC) geeignet. Für MC mit hohen Anteil von Füllstoffen sind Laserpulse im Nanosekundenbereich gut geeignet, denn durch den thermischen Abtragungsprozeß werden die Füllerteilchen zerschlagen und überlagern sich nicht mit weiterer Abtragung. Die Pikosekunden Laserquelle im Infraroten und Grünen Lichtbereich eigneten sich besser für MC Abtragung, verursachten aber tiefe Löcher in Silizium. Dies ist das Hauptproblem von Pikosekundenlaser. Der in FULL CONTROL benutzte Exzimerlaser zeigte keine deutliche Siliziumabtragung. Der Exzimerlaser konnte das MC gut abtragen, erzeugte aber eine große "Heat Affected Zone (HAZ)" Für die Abtragung von Si-Chipstapel mit DPSS (Diode Pumped Solid State) Laser ist die Wellenlänge entscheidend. Mit dem 355 nm DPSS Laser war eine deutliche Siliziumabtragung mit einer Oberflächenrauigkeit von etwa 5 µm

möglich. Aufgrund der geringen sichtbaren Schäden im µm-Bereich erzielte dieser Laser die besten Ergebnisse für Zielpräparation von SiP Aufbauten. In Tabelle 2 sind die Untersuchungen zu Laserablation zusammengefasst (Refs. [6,8]).

Tabelle 2: Zusammenfassung der Ergebnisse für Laserablation wichtiger SiP Materialien wie Silizium, MC und bestimmter Metalle (Cu/Au) (siehe Referenzen

[6,8]).

|                            | Material     |          |       |

|----------------------------|--------------|----------|-------|

| Laser Source               | Moldcompound | Silizium | Cu/As |

| Femtosekunden Laser        | -            | +        | ++    |

| Pikosekunden Laser 1030 nm | +            | -        | -     |

| Pikosekunden Laser 515 nm  | +            | -        | +     |

| Exzimerlaser 248 nm        | ++           | -        | +     |

| DPSS 1064 nm               | ++           | -        | -     |

| DPSS 532 nm                | ++           | +        | +     |

| DPSS 355 nm                | ++           | ++       | ++    |

# 1.4.2 Freilegung von IC Oberflächen in Gehäusestapel durch Micro-abrasive Blasting

In diesem Abschnitt wird das mikro-abrasive Druckluftstrahlen (engl. *Micro-abrasive blasting*, MAB) als komplementäre Präparationsmethode zum Freilegen von IC-Strukturen in SiPs mit gestapelten Siliziumchips beschrieben, welche im Rahmen von FULL CONTROL entwickelt wurde. Dieses ist nicht nur notwendig, um Zugang zu den IC-Strukturen zur Fehleranalyse zu erhalten. Auch für die zerstörungsfreien Lokalisierungsverfahren wie Infrarot-Thermografie und magnetische Bildgebung kommt es mit einer zunehmenden Anzahl von gestapelten Chips bzw. mit zunehmendem Arbeitsabstand zu einer signifikant reduzierten Auflösung.

Die im Abschnitt zuvor beschriebene Laserpräparation erlaubt zwar die Herstellung von Querschnitten in ausgezeichneter Qualität ebenso wie den sehr gleichmäßigen flächigen Abtrag mehrerer gestapelter Siliziumchips. Allerdings ist der Laserabtrag trotz der geringen Oberflächenrauigkeit nicht geeignet um die Präparation gezielt in der Klebeschicht zu stoppen. Wie sich bei der Ermittlung der Abtragraten gezeigt hat, hat die Polymermatrix der Klebefolie eine rund 50-fach höhere Abtragsrate als Silizium. Somit wird die 25  $\mu m$  dicke Klebefolie in Sekundenbruchteilen abgetragen und die darunterliegenden IC-Strukturen beschädigt.

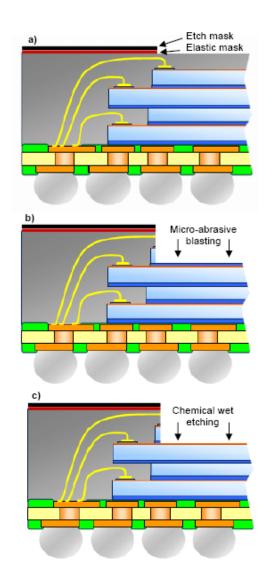

Der Prozessablauf für das Freilegen von IC-Strukturen in einem SiP ist nachfolgend gezeigt. Zunächst werden zwei unterschiedliche Maskierschichten auf dem Bauteil befestigt. Die unterste Maskierschicht ist ein Aluminium-Klebeband, das als Ätzmaske beim chemischen Entfernen verhindert, dass die umliegende Vergussmasse ebenfalls abgetragen wird. Darüber wird als obere Maskiermaske ein elastisches Klebeband befestigt, welches den Bereich des mikro-abrasiven Druckluftstrahlens festlegt. Alle Bereiche unterhalb dieser elastischen Maskierung werden vom mikro-abrasiven Druckluftstrahlen nicht angegriffen.

Nach der Maskierung erfolgt das mikro-abrasive Druckluftstrahlen auf der Bauteiloberfläche. Bei einem Düsenabstand von 120 *mm* und einen Luftdruck von 2

bar wird 20  $\mu m$  Vergussmasse bzw. 12  $\mu m$  Silizium pro Sekunde abgetragen. Nach dem Erreichen der Klebefolie unter dem obersten Siliziumchip wird diese mit rund 0,6  $\mu m/s$  abgetragen. Die Klebefolie würde also für rund 40 s den abrasiven Partikeln widerstehen.

Nach dem kompletten Abtrag von Vergussmasse und obersten Siliziumchip wird das mikro-abrasive Druckluftstrahlen allerdings gestoppt und die Klebefolie chemisch entfernt (Abbildung 28). Dies geschieht mit auf 60 °C erwärmter Salpetersäure. Nach wenigen Sekunden zeigt die Klebefolie ein blasenartiges Anschwellen und kann mit einer Pinzette entfernt werden. Alternativ kann die Klebefolie auch komplett mit Salpetersäure aufgelöst werden.

Abbildung 28: Prozessablauf für das Freilegen von IC-Strukturen in einem SiP mit gestapelten Siliziumchips: (a) Aufkleben zweier Maskierschichten; (b) Abtrag der Vergussmasse und des obersten Siliziumchips; (c) Chemisches Auflösen der Klebefolie mit Salpetersäure.

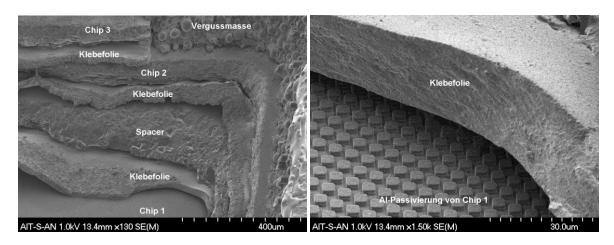

Das mikro-abrasive Druckluftstrahlen zum Abtragen des Siliziumchips innerhalb weniger Sekunden sowie das chemische Entfernen der Klebeschicht können nun

zum schichtweisen Abtrag weiterer gestapelter Siliziumchips verwendet werden. Das Resultat mehrerer solcher alternierender Durchgänge ist in Abbildung 29 gezeigt. In einer Ecke des Bearbeitungsfeldes sind drei abgetragenen Siliziumchips und die dazwischen liegenden Klebeschichten erkennbar. Abbildung 29 zeigt die unterste Klebefolie sowie den untersten freigelegten Siliziumchip mit unversehrter Aluminiumpassivierung. Die unbeschädigten IC-Strukturen sind nun zugänglich für weitere Untersuchungen oder zur Fehleranalyse.

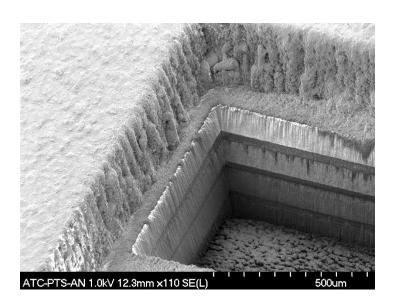

Abbildung 29: (a) REM-Aufnahme einer Ecke des Bearbeitungsfelds; (b) Detailaufnahme der untersten Klebefolie und der unbeschädigten Aluminiumpassivierung des freigelegten Siliziumchips.

Zusammenfassend lässt sich sagen, dass das mikro-abrasive Druckluftstrahlen eine schnelle, zuverlässige und preisgünstige Methode zum Freilegen von IC-Strukturen in SiPs mit gestapelten Siliziumchips ist. Die Gerätekosten sind minimal und die Bedienung ist auch durch unerfahrene Anwender möglich, da die freizulegenden Strukturen vom der elastischen Klebefolie geschützt sind. Ein bedeutender Vorteil ist weiterhin, dass die Verwölbung des Halbleitergehäuses bzw. der Siliziumchips keinen Einfluss auf das Präparationsresultat hat.

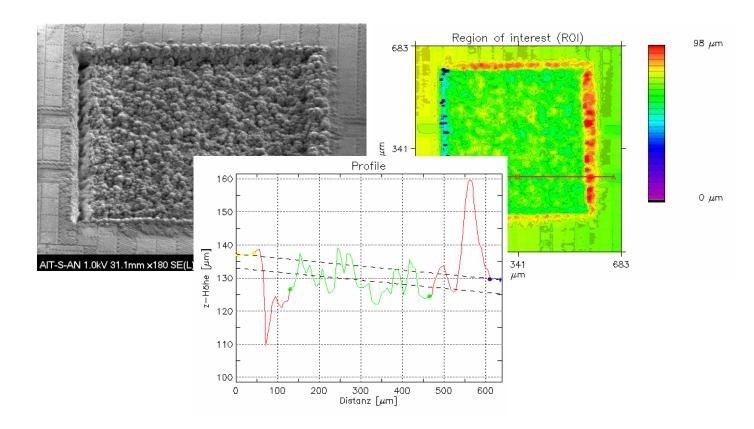

Der bisherige Stand der Technik, nämlich das planparallele Schleifen kombiniert mit Plasmaätzen oder chemischem Ätzen ist weitaus zeitaufwändiger, kostenintensiver und benötigt zudem sehr erfahrene Anwender als das mikro-abrasive Druckluftstrahlen [Referenz 4+5]. Für das Freilegen von einzelnen gestapelten Siliziumchips, welches mit reiner Laserpräparation nicht möglich ist, steht dank FULLCONTROL auch für diesen Sonderfall eine geeignete artefaktfreie Präparationsmethode zur Verfügung. Abbildung 30 unten zeigt die Messung der Abtragungstiefe mittels eines Profilometers.

Abbildung 30: Messung der Abtragungstiefe mittels eines Profilometers.

## 1.4.3 FIB Präparationstechnik für hochauflösend Untersuchungen (AP3.3, AP3.4)

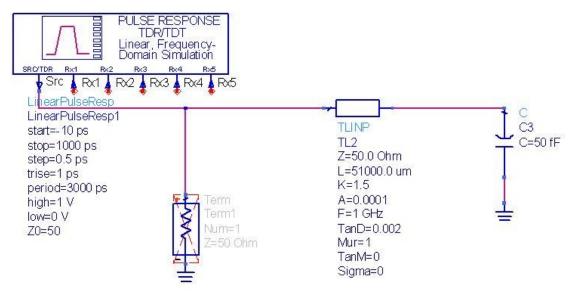

#### Gerätekonzept für die Implementierung der Laserablation in die CrossBeam-Technologie

Von Carl Zeiss NTS und Infineon wurde ein Gerätekonzept zur Implementierung der Laserablation in die Cross-Beam-Technologie entwickelt. Dieses ist unabhängig von der spezifischen Laserquelle. Wesentliches Merkmal ist die Trennung von Laserquelle und FIB-Kammer zur Schwingungsvermeidung.

#### Laser-Präparation bzw. FIB-Laser-Integration

Wesentlich für die spätere Bedienbarkeit des neuen Geräts wird die Navigation auf der Probe sein, um eine zuverlässige Fehlerpräparation zu gewährleisten. Aus diesem Grunde wurden Carl Zeiss NTS von Infineon kompliziert aufgebaute SiP-Bauteil (10x SiP System-in-Package 4-fach-Stack und 5x FCWB FlipChip WireBond) mit definierten Fehlern zur Verfügung gestellt. Zusammen mit von Infineon hergestellten hochaufgelösten Röntgenaufnahmen wurde an diesen Bauteilen die Navigation auf den Bauteilen bzw. Navigation mittels Röntgenbildern in die Steuerung des Demonstrators integriert.

Abb. 31: Röntgenaufnahmen von SiP-Aufbauten mit definierten Fehlern.

In Abstimmung mit den Projektpartnern Carl Zeiss NTS und Fraunhofer IWMH wurde die Evaluation des Demonstrators der FIB-Laser-Integration abgestimmt. Dabei wurde die in Abbildung 32 dargestellte Matrix der geplanten Erprobungen ausgearbeitet.

Zum einen sollten das Abtragsverhalten und die Wärmeeinflusszonen an den reinen Package-Materialien wie z. B. Leadframes, Bonddrähten, Lotmaterialien usw. ermittelt werden. Zum anderen sollte dies auch in komplexen SiP-Systemen geschehen um die Auswirkungen und Einflüsse auf die Fehlerlokalisation im Gesamtsystem zu erfassen.

Erste Voruntersuchungen wurden von Infineon durchgeführt, um einzelne Messmethoden wie z. B. die Erfassung von laserinduzierten Störstellen im Siliziumkristallgitter mittels XRT (Röntgen-Topographie) für Anwendungen auf komplette SiP-Systeme zu qualifizieren.

Die Konstruktion und die Fertigung der einzelnen Komponenten für den Demonstrator der FIB-Laser-Integration beim Projektpartner Carl Zeiss NTS wurde abgeschlossen inkl. der Konstruktion der Laserbearbeitungskammer mit Schleuse, Laserfenster, Vakuumsystem und Gaseinlässen. Nachdem von Carl Zeiss NTS der Laser zum ersten Mal in Betrieb genommen wurde, wurden gemeinsame Versuchsdurchführungen von Infineon und Carl Zeiss NTS zur Evaluation des Demonstrators der FIB-Laser-Integration gemacht.

| Reine Materialien:                                                |                                                                                                                                                              |                                                                                                                        |                                    |                                                   |                        |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------|------------------------|

| Material:                                                         | Ziel der Untersuchung:                                                                                                                                       | Vorgehensweise:                                                                                                        | Material geliefert von:            | Methoden:                                         | VVo:                   |

| Golddraht (geglüht /<br>ungeglüht) HA; Ø > 30<br>um               | Wärmeinflusszone (WEZ) in<br>Au bestimmen                                                                                                                    | Draht auf Träger befestigen><br>durchlasern> Analyse                                                                   | IVMH                               | FIB-CS, Channeling-<br>Kontrast, EBSD?            | IVM Halle<br>(Zeiss)   |

| Kupfer Leadframe /<br>eventuell verzinnt                          | Wärmeinflusszone (WEZ) in<br>massiven Cu bestimmen                                                                                                           | Leadframe durchlasern                                                                                                  | Infineon Rgb                       | FIB-CS, Channeling-<br>Kontrast, EBSD?            | M/M Halle<br>(Zeiss)   |

| Lote / Lotballs / standard<br>bleifrei Lot / eventuell im<br>FCWB | WEZ im Lot bestimmen                                                                                                                                         | Lot ball durchlasern                                                                                                   | Infineon Rgb                       | FIB-CS, Channeling-<br>Kontrast, EBSD?            | M/M Halle<br>(Zeiss)   |

| Silizium                                                          | guantitative Ausdehnung<br>der WEZ (Aufschmelz-<br>zone, Versetzungen) als<br>Funktion der<br>Laserparameter                                                 | Matrix verschiedener<br>Laserparameter auf<br>unprozessierten Si-Wafer lasern                                          | Infineon Rgb<br>(Vorversuch läuft) | XRT - X-Ray<br>Topography                         | Infineon Mch           |

| Materialsysteme:                                                  |                                                                                                                                                              |                                                                                                                        |                                    |                                                   |                        |

| Materialsystem:                                                   | Ziel der Untersuchung:                                                                                                                                       | Vorgehensweise:                                                                                                        | Material geliefert von:            | Methoden:                                         | VVo:                   |

| Au-Bondpad                                                        | WEZ in Bondpad bestimmen<br>- Gefüge wohl gleichmäßig<br>in der Tiefe verteilt, in<br>lateraler Richtung dürfte<br>Gefügeänderung besser<br>ermittelbar sein | Bondpad mit Laser freischneiden                                                                                        | Infineon Rgb                       | Channeling-Kontrast,<br>EBSD?                     | IV/M Halle<br>(Zeiss)  |

| Au-Bondpad mit<br>Golddrahtbond<br>(gemoldet)                     | Laser CS durch<br>Drahtbondverbindung                                                                                                                        | Rechteck versetzt auf Reihe von<br>Bondverbindugen lasern> CS<br>an unterschiedlichen Positionen                       | Infineon Rgb                       | Channeling-Kontrast,<br>EBSD?                     | M/M Halle<br>(Zeiss)   |

| Cu-Meanderstrukturen<br>auf Testchip in Stacked<br>Package        | WEZ auf strukturiertem Chip<br>bestimmen                                                                                                                     | CS senkrecht zu 0,5 µm bzw. 3<br>µm breiten Cu-Linien - WEZ in den<br>verbleibenden 150 µm Cu-<br>Leiterbahn bestimmen | Infineon Rgb                       | FIB CS, Channeling-<br>Kontrast, EBSD?            | IIV/M Halle<br>(Zeiss) |

| Stacked Package                                                   | WEZ in Si auf strukturiertem<br>Chip bestimmen                                                                                                               | Laser CS durch Stacked Package<br>anfertigen> einbetten><br>Schliff dünnen                                             | Infineon Rgb<br>(Vorversuch läuft) | XRT - X-Ray<br>Topography an<br>gedünntem Schliff | Infineon Mch           |

Abbildung 32: Aufstellung der geplanten Erprobungen am Demonstrator der FIB-Laser-Integration (mit Carl Zeiss NTS und Fraunhofer IWMH abgestimmt).

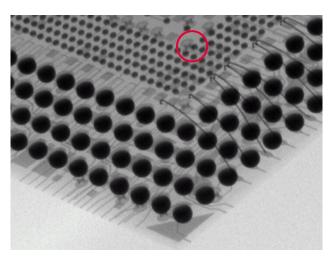

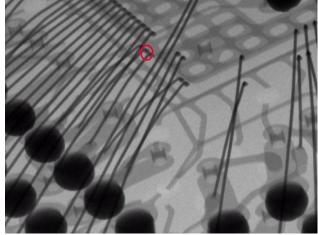

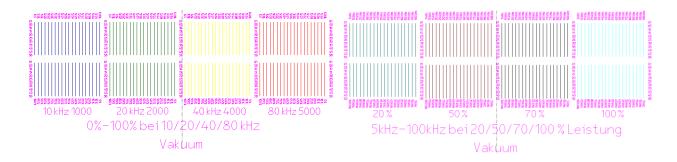

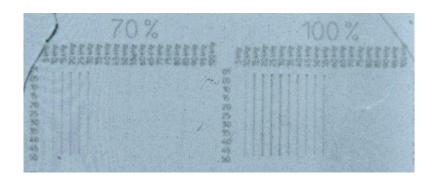

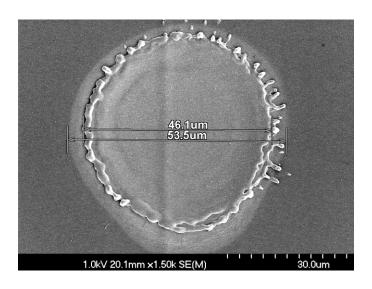

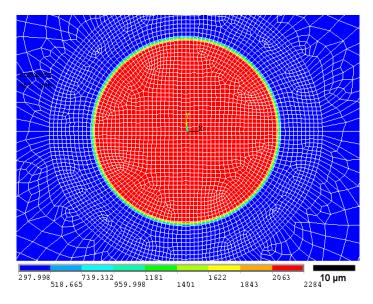

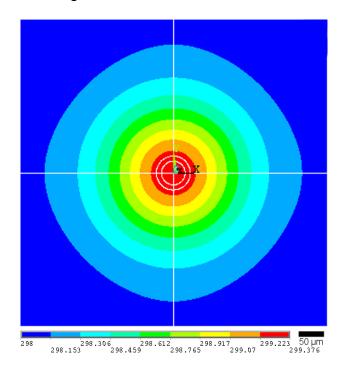

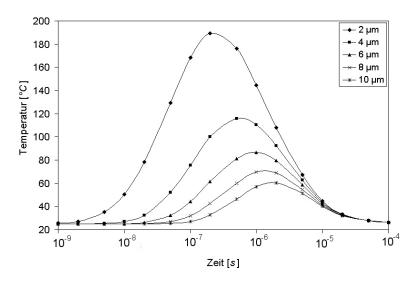

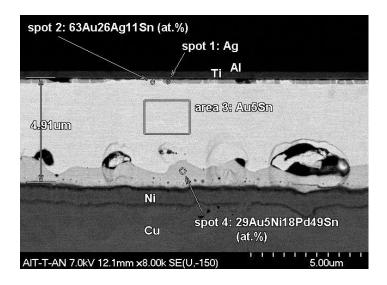

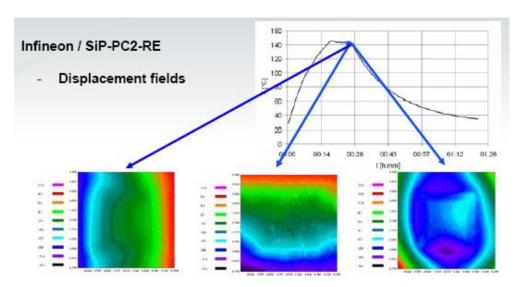

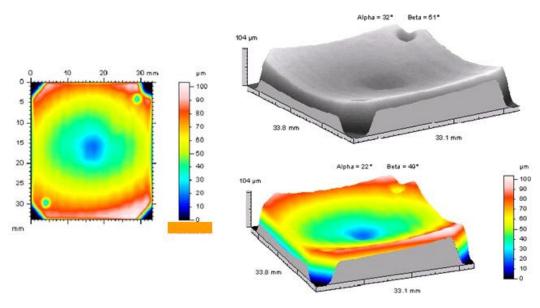

Bei den Versuchen wurden auf reinem Package-Material, wie z. B. Silizium und Leadframe-Kupfer, Matrizen mit variierten Laserparametern (Laserleistung, Pulsfrequenz) gelasert (Abb. 31). Ziel war es, die Schädigungszone durch die laserinduzierte Wärme (engl. Heat-Affected-Zone HAZ) zu bestimmen und mit den Laserparametern zu korrelieren. Die Kenntnis von der Größe der Schädigungszone im SiP ist ausgesprochen wichtig, da diese gleichbedeutend ist mit der Materialmenge, die bei der anschließenden FIB-Präparation abgetragen werden muss. Das ist wiederum der bedeutendste Faktor für die Gesamtprozesszeit. Des Weiteren wurden auch Laserversuche an kompletten SiP-Bauteilen durchgeführt.